Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Дипломная работа: 8-разрядные КМОП RISC микроконтроллеры с внутрисистемно программируемым Flash ПЗУ

Дипломная работа: 8-разрядные КМОП RISC микроконтроллеры с внутрисистемно программируемым Flash ПЗУ

Южно-Уральский государственный университет

Заочный инженерно - экономический факультет

Контрольная (курсовая) работа №3

По Информатике

Выполнил студент- заочник 2го курса

Шифр – ЭПА-04-588

Группа – 247

«____»___________2009г. «____»___________2009г.

Срок предоставления работы по графику Дата отправки работы

№_____________ по журналу «____»___________2009г.

___________________ Хусаинов Р.З.

отметка о зачете работы

Преподаватель

____________________

Подпись преподавателя

«____»_____________2009г.

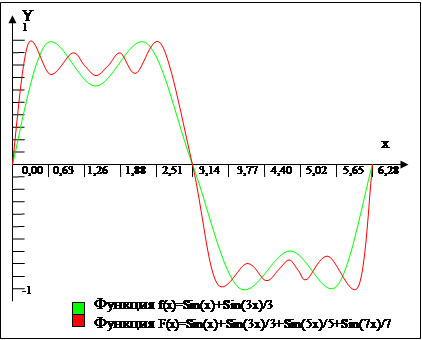

1. Построить два графика в одной координатной сетке: функция f(x)=Sin(x)+Sin(3x)/3 и F(x)=Sin(x)+Sin(3x)/3+Sin(5x)/5+Sin(7x)/7. Диапазон изменения переменной х Є[0;6.28]. На графике вывести обозначение масштабов переменных, вывести название графика.

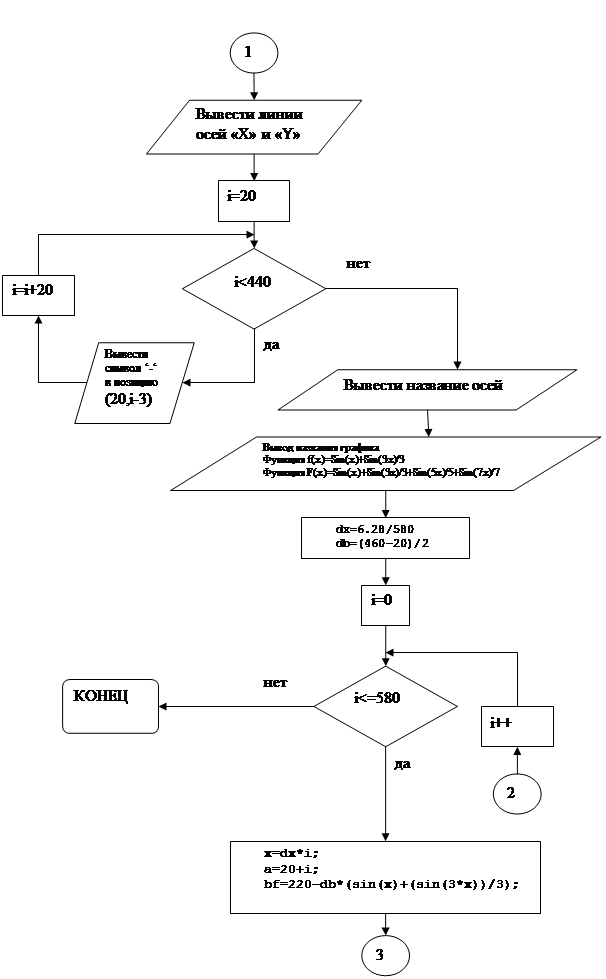

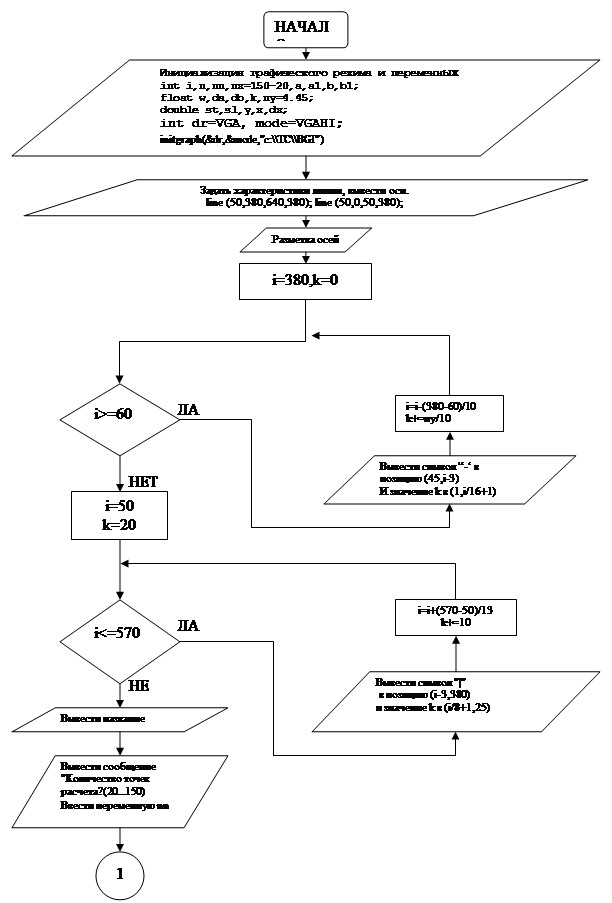

Программа:

/* Программа построения графиков функции*/

/* F(x)=Sin(x)+Sin(3x)/3+Sin(5x)/5+Sin(7x)/7*/

/* и f(x)=Sin(x)+Sin(3x)/3*/

#include <conio.h>

#include <graphics.h>

#include <math.h>

void main()

{

/* Инициализация графического режима и переменных*/

int i,a,bf=220,bF=220;

float x,db;

double dx;

int dr=VGA, mode=VGAHI;

initgraph(&dr,&mode,"c:\\TC\\BGI");

/*initgraph (&dr,&mode,"G:\\lang\\tc\\bgi");*/

/* Прорисовка осей*/

setbkcolor(BLACK); setlinestyle(0,0,2);

line (20,220,640,220); /*X*/

moveto (630,218);lineto(640,220);lineto(630,222);lineto(630,218);

line (20,0,20,440); /*Y*/

moveto (20,0);lineto(18,10);lineto(22,10);lineto(20,0);

/*Разметка осей*/

setcolor (WHITE);

for(i=20;i<440;i=i+20)

{outtextxy (20,i-3,"-");}

outtextxy (30,420,"-1");

outtextxy (30,20,"1");

outtextxy (32,2,"Y");

outtextxy (630,205,"X");

/* Название графика*/

setfillstyle (1,GREEN);

bar (50,435,68,445);

settextstyle (6,0,1);

outtextxy (80,429,"-Функция f(x)=Sin(x)+Sin(3x)/3");

setfillstyle (1,RED);

bar (50,455,68,465);

outtextxy (80,450,"-Функция F(x)=Sin(x)+Sin(3x)/3+Sin(5x)/5+Sin(7x)/7");

/*Определение приращения (x) и координат по осям*/

dx=6.28/580; /*dx с шагом в 1 пиксель по х*/

db=(460-20)/2;

/*Построение графика Sin(x)+(Sin(3x))/3*/

moveto (20,220);

for (i=0;i<=580;i++)

{

setlinestyle(0,0,4);

setcolor(GREEN);

x=dx*i;

a=20+i;

bf=220-db*(sin(x)+(sin(3*x))/3);

lineto(a,bf); /*Рисуем f(х)*/

moveto(a,bF); /*Переходим к F(x)*/

/*Построение графика Sin(x)+(Sin(3x))/3+(Sin(5x))/5+(Sin(7x))/7*/

setcolor(RED);

bF=220-db*(sin(x)+(sin(3*x))/3+(sin(5*x))/5+(sin(7*x))/7);

lineto(a,bF); /*Рисуем F(х)*/

moveto(a,bf); /*Переходим к f(x)*/

/*Ставим метку по оси Х*/

if(i%(580/10)==0)

}

getch();

closegraph();

}

Пример исполнения:

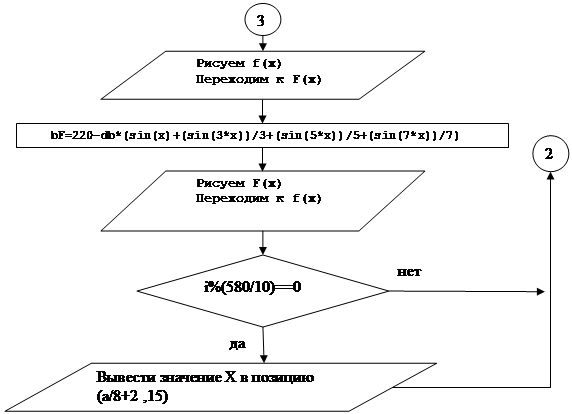

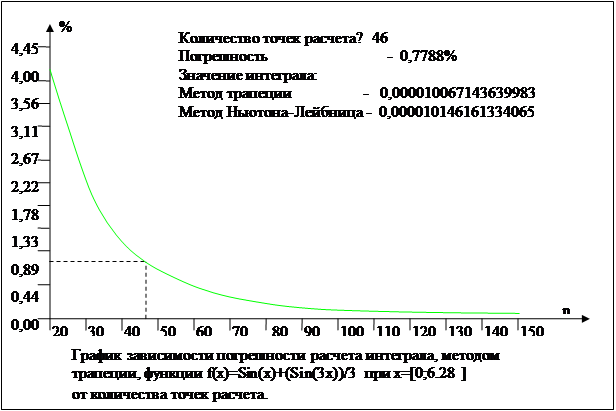

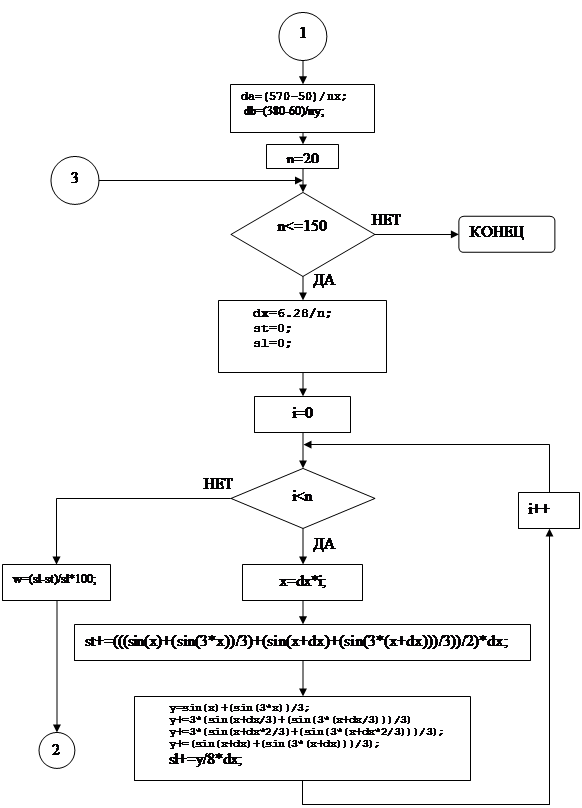

2.Выполнить расчет определенного интеграла функции f (x)=Sin(x)+(Sin(3x))/3 методом трапеции. Диапазон изменения переменной х=[0;6.28]. Построить график зависимости погрешности расчета интеграла от количества точек расчета N=20…150. Истинное значение рассчитывается с помощью формулы Ньютона-Лейбница.

Программа:

/*Программа построения графика зависимости погрешности расчета интеграла*/

/* функции f(x)=Sin(x)+(Sin(3x))/3 при х=[0;6.28], методом трапеции, */

/* от количества точек расчета 'n'=20...150 */

#include <conio.h>

#include <math.h>

#include <graphics.h>

void main()

{

/* Инициализация графического режима и переменных*/

int i,n,nn,nx=150-20,a,a1,b,b1;

float w,da,db,k,ny=4.45;

double st,sl,y,x,dx;

int dr=VGA, mode=VGAHI;

initgraph(&dr,&mode,"c:\\TC\\BGI");

/*initgraph (&dr,&mode,"G:\\lang\\tc\\bgi");*/

/* Прорисовка осей*/

textcolor(7); setcolor(7); setbkcolor(BLACK); setlinestyle(0,0,2);

line (50,380,640,380); /*X*/

moveto (630,382);lineto(640,380);lineto(630,378);lineto(630,382);

line (50,0,50,380); /*Y*/

moveto (50,0);lineto(48,10);lineto(52,10);lineto(50,0);

/*Разметка осей*/

/*По оси 'Y'*/

for(i=380,k=0;i>=60;i=i-(380-60)/10,k+=ny/10)

{

outtextxy (45,i-3,"-");

gotoxy (1,i/16+1);

printf ("%3.2f",k);

}

/*По оси 'X'*/

for(i=50,k=20;i<=570;i=i+(570-50)/13,k+=10)

outtextxy (62,8,"%");

outtextxy (630,360,"n");

/*Название графика*/

settextstyle(6,0,2); setcolor(7);

outtextxy(10,420,"График зависимости погрешности расчета интеграла, методом");

outtextxy(10,438,"трапеции, функции f(x)=Sin(x)+(Sin(3x))/3 при х=[0;6.28]");

outtextxy(10,456,"от количества точек расчета.");

outtextxy(160,8,"Количество точек расчета?(20...150)-");

gotoxy(70,2); scanf("%d",&nn);

/*Определение приращения по осям*/

da=(570-50)/nx;

db=(380-60)/ny;

/*Расчет итеграла f(x)=Sin(x)+(Sin(3x))/3*/

for(n=20;n<=150;n++)

{

dx=6.28/n;

st=0;sl=0;

for(i=0;i<n;i++)

{

x=dx*i;

/*методом трапеции*/

st+=(((sin(x)+(sin(3*x))/3)+(sin(x+dx)+(sin(3*(x+dx)))/3))/2)*dx;

/*методом Ньютона-Лейбница*/

y=sin(x)+(sin(3*x))/3;

y+=3*(sin(x+dx/3)+(sin(3*(x+dx/3)))/3);

y+=3*(sin(x+dx*2/3)+(sin(3*(x+dx*2/3)))/3);

y+=(sin(x+dx)+(sin(3*(x+dx)))/3);

sl+=y/8*dx;

}

/*Расчет погрешности*/

w=(sl-st)/sl*100;

if(n==nn)

{

setcolor(7);

outtextxy(160,24,"Погрешность");

gotoxy(56,3);

printf("- %6.4f%",w);

outtextxy(80,24*2,"Значение интеграла:");

outtextxy(160,24*3,"метод трапеции");

gotoxy(53,6);

printf("- %+20.18f",st);

outtextxy(160,24*4-8,"метод Ньютона-Лейбница");

gotoxy(53,7);

printf("- %+20.18f",sl);

}

/*Вывод в график*/

setlinestyle(0,1,1);setcolor(GREEN);

a=50+da*(n-20);

b=380-db*w;

if(n==20){a1=a;b1=b;}

else {line(a,b,a1,b1); a1=a; b1=b;}

if(n==nn)

{

setlinestyle(1,1,1);setcolor(7);

moveto(a,b);lineto(a,380);moveto(a,b);

lineto(50,b);moveto(a,b);

}

}

getch();

closegraph();

}

Пример исполнения:

Алгоритм:

1. Высокопроизводительные 8-разрадные RISC микроконтроллеры семейства AT90S AT90S\LS8535 и AT mega8535 фирмы Atmel Corporation: параметры , архитектура, система команд.

AT mega8535

AT mega8535L

8-разрядные КМОП RISC микроконтроллеры с внутрисистемно программируемым Flash ПЗУ

Общие сведения

Как и все микроконтроллеры AVR фирмы «Atmel», микроконтроллеры семейства Mega являются 8-разрядными микроконтроллерами, предназначенными для встраиваемых приложений. Они изготавливаются по малопотребляющей КМОП-технологии, которая в сочетании с усовершенствованной RISC - архитектурой позволяет достичь наилучшего соотношения быстродействие/энергопотребление. Контроллеры описываемого семейства являются наиболее развитыми представителями микроконтроллеров AVR.

Отличительные особенности

К числу особенностей микроконтроллеров AVR семейства Mega относятся:

• FLASH-память программ объемом 8 Кбайт (число цикле стирания/записи не менее 1000);

• оперативная память (статическое ОЗУ) объемом 512 байт;

• память данных на основе ЭСППЗУ (EEPROM) объем 512 байт (число циклов стирания/записи не мене 100000);

• возможность защиты от чтения и модификации памяти программ и данных;

• возможность программирования непосредственно в системе через последовательные интерфейсы SPI и JTAG;

• возможность самопрограммирования;

• возможность внутрисхемной отладки в соответствии со стандартом IEEE 1149.1 (JTAG);

• различные способы синхронизации: встроенный RC-генератор с внутренней или внешней времязадающей RC-цепочкой или с внешним резонатором (пьезокерамическим или кварцевым); внешний сигнал синхронизации;

• наличие нескольких режимов пониженного энергопотребления;

• наличие детектора снижения напряжения питания (brown-out detector,BOD);

• возможность программного снижения частоты тактового генератора.

Характеристики процессора

Подавляющее большинство основных характеристик процессора микроконтроллеров семейства Mega такие же, что и у микроконтроллеров других семейств — Classic и Tiny:

• полностью статическая архитектура; минимальная тактовая частота равна нулю;

• АЛУ подключено непосредственно к регистрам общего назначения;

• многоуровневая система прерываний; поддержка очереди прерываний.

В то же время процессор микроконтроллеров семейства Mega имеет ряд характеристик, присущих именно этому семейству:

• 130 команд, большинство команд выполняются за один машинный цикл;

• 17 внутренних+3 внешних источников прерываний;

• наличие программного стека во всех моделях семейства;

• наличие аппаратного умножителя.

Характеристики подсистемы ввода/вывода

Все характеристики подсистемы ввода/вывода микроконтроллеров семейства Mega такие же, как и у микроконтроллеров других семейств:

• программное конфигурирование и выбор портов ввода/вывода;

• выводы могут быть запрограммированы как входные или как выходные независимо друг от друга;

• входные буферы с триггером Шмитта на всех выводах;

• возможность подключения ко всем входам внутренних подтягивающих резисторов (сопротивление резисторов составляет 35...120кОм).

Периферийные устройства

Микроконтроллеры семейства Mega имеют наиболее богатый набор периферийных устройств (ПУ). При этом в большинстве моделей имеются все ПУ, которые вообще встречаются в составе микроконтроллеров AVR. Этими устройствами являются:

• 2а 8-разрядных таймера/счетчика (таймеры ТО и Т2

• 16-разрядный таймер/счетчик (таймер ТЗ);

• 4 генератора сигнала с ШИМ разрядностью 8 бит (один из режимов работы 8-разрядных таймеров/счетчиков ТО и Т2);

• аналоговый компаратор;

• многоканальный 10-разрядный АЦП как с несимметричными, так и с дифференциальными входами;

• полнодуплексный универсальный синхронный/асинхронный приемопередатчик (USART);

• последовательный синхронный интерфейс SPI;

• последовательный двухпроводный интерфейс TWI (аналог интерфейса 12С).

Архитектура ядра

Ядро микроконтроллеров AVR семейства Mega выполнено по усовершенствованной RISC-архитектуре (enhanced RISC). Арифметико-логическое устройство (АЛУ), выполняющее все вычисления подключено непосредственно к 32-м рабочим регистрам, объединенным в регистровый файл. Благодаря этому АЛУ выполняет одну операцию (чтение содержимого регистров, выполнение операции и запись результата обратно в регистровый файл) за один машинным цикл. Практически каждая из команд (за исключением команд у которых одним из операндов является 16-разрядный адрес) занимает одну ячейку памяти программ.

AT90S8535

AT90LS8535

8-разрядные КМОП RISC

микроконтроллеры с внутрисистемно программируемым Flash ПЗУ

Отличительные особенности

• AVR RISC архитектура - архитектура высокой производительности и малого потребления

• 118 команд, большинство которых выполняется за один машинный цикл

• 8 Кбайт Flash ПЗУ программ, с возможностью внутрисистемного перепрограммирования и загрузки через SPI последовательный канал,1000 циклов стирание/запись

• 512 байтов ЭСППЗУ данных, с возможностью внутрисистемного перепрограммирования и загрузки через SPI последовательный канал, 100000 циклов стирание/запись

• 512 байтов встроенного СОЗУ

• 32 x 8 бит регистра общего назначения

• 32 программируемые линии ввода/вывода

• 8-канальный 10-разрядный аналого-цифровой преобразователь

• 16-разрядный и 32-разрядный формат команд

• Программируемый полный дуплексный UART

• Диапазон напряжений питания от 2,7 В до 6,0 В (AT90LS8535) и от 4,0 В до 6,0 В (AT90S8535)

• Полностью статический прибор - работает при тактовой частоте от 0 Гц до 8 МГц

(AT90S8535) и при тактовой частоте от 0 Гц до 4 МГц (AT90LS8535)

• Производительность до 8 MIPS при частоте 8 МГц

• Два 8-разрядных таймера/счетчика с отдельным прескалером и режимом сравнения

• 16-разрядный (с режимами сравнения и захвата) таймер/счетчик с отдельным прескалером

• Три ШИМ канала

• Внешние и внутренние источники сигналов прерывания

• Программируемый сторожевой таймер с собственным встроенным генератором

• Встроенный аналоговый компаратор

• Встроенные часы реального времени с собственным встроенным генератором и режимом счетчика

• Блокировка режима программирования

• Режимы энергосбережения: пассивный (idle), экономичный (power save) и стоповый(power down)

• Встроенная схема сброса по подаче питания

• Промышленный (-40°C...85°C) и коммерческий (0°C...70°C) диапазоны температур

• 40-выводной корпус PDIP и 44-выводные PLCC и TQFP

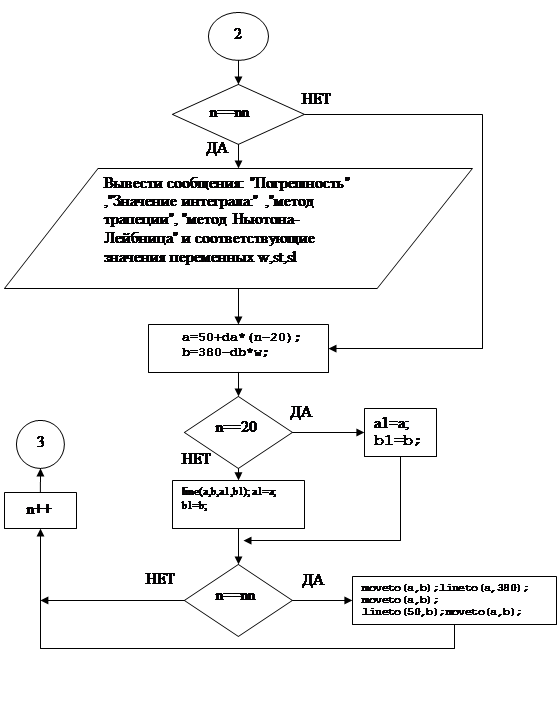

Архитектура микроконтроллеров семейства Mega

Микроконтроллеры AVR семейства Mega являются 8-разрядными микроконтроллерами с RISC-архитектурой. Они имеют электрически стираемую память программ (FLASH) и данных (EEPROM), а также разнообразные периферийные устройства. Следует отметить, что микро контроллеры семейства Mega имеют самый богатый набор периферийных устройств по сравнению с микроконтроллерами других семейств. Более того, состав этих устройств от модели к модели практически не меняется (меняются только их функциональные возможности). К устройствам, присутствующим не во всех моделях семейства, относятся АЦП, модуль двухпроводного интерфейса TW1 (Two Wire Interface, аналог шины 12С), а также модуль интерфейса JTAG. Структурная схема микроконтроллеров семейства Mega приведена на Рис.

Организация памяти

В микроконтроллерах AVR реализована Гарвардская архитектура, в соответствии с которой разделены не только адресные пространства памяти программ и памяти данных, но также и шины доступа к ним. Способы адресации и доступа к этим областям памяти также различны. Такая структура позволяет центральному процессору работать одновременно как с памятью программ, так и с памятью данных, что существенно ограничивает производительность. Каждая из областей памяти данных (ОЗУ и EEPROM) также расположена в своем адресном пространстве.

Память программ

Память программ предназначена для хранения команд, управляющих функционированием микроконтроллера. Память программ также часто используется для хранения таблиц констант, не меняющихся во время работы программы.

Как уже было сказано, память программ представляет собой электрически стираемое ППЗУ (FLASH-ПЗУ). В связи с тем что длина всех команд кратна одному слову (16 бит), память программ имеет 16-разрядную организацию. Соответственно, объем памяти микроконтроллеров семейства составляет 8К (8x1024) 16-разрядных слов. Логически память программ разделена на две неравные части — область прикладной программы и область загрузчика. В последней может располагаться специальная программа (загрузчик), позволяющая микроконтроллеру самостоятельно управлять загрузкой и выгрузкой прикладных программ. Если же возможность самопрограммирования микроконтроллера не используется, прикладная программа может располагаться и в области загрузчика.

Для адресации памяти программ используется счетчик команд (PC — Program Counter). Размер счетчика команд составляет 12разрядов

По адресу $0000 памяти программ находится вектор сброса. После инициализации (сброса) микроконтроллера выполнение программы начинается с этого адреса (по этому адресу должна размещаться команда перехода к инициализационной части программы). Начиная с адреса $001 памяти программ, располагается таблица векторов прерываний. Размер этой области 20 байт ($001…$014).

При возникновении прерывания после сохранения в стеке текущего значения счетчика команд происходит выполнение команды, расположенной по адресу соответствующего вектора. Поэтому по этим адресам располагаются команды перехода к подпрограммам обработки прерываний. В качестве этих команд используются команды относительного перехода (RJMP.

Если прерывания в программе не используются либо таблица векторов прерываний располагается в области загрузчика, то основная программа может начинаться непосредственно с адреса $0001.

Как известно, память программ может использоваться не только для хранения кода программы, но также и для хранения различных констант. Для пересылки байта из памяти программ в память данных имеется специальная команда — LPM. При использовании команды LPM адрес, по которому производится чтение, определяется содержимым индексного регистра Z. При этом старшие 15 разрядов содержимого регистра будут определять адрес слова (0...32К), а младший разряд будет определять, какой из байтов будет прочитан: «О» — младший байт, «1» — старший байт

В заключение следует отметить, что FLASH-ПЗУ, используемое в микроконтроллерах AVR, рассчитано как минимум на 1000 циклов стирания/записи.

Память данных

Память данных микроконтроллеров разделена на три части: регистровая память, оперативная память (статическое ОЗУ) и энерго независимое ЭСППЗУ (EEPROM).

Регистровая память включает 32 регистра общего назначения (РОН), объединенных в файл, и служебные регистры ввода/вывода (РВВ).

В обеих областях регистров ввода/вывода располагаются различные служебные регистры (регистр управления микроконтроллером, регистр состояния и т. п.), а также регистры управления периферийными устройствами, входящими в состав микроконтроллера

Для хранения переменных программ помимо регистров общего назначения также может использоваться статическое ОЗУ объемом 512 байт.

Для долговременного хранения различной информации, которая может изменяться в процессе функционирования готовой системы (калибровочные константы, серийные номера, ключи и т. п.), в микроконтроллерах используется EEPROM-память. Ее объем составляет 512 байт. Эта память расположена в отдельном адресном пространстве, а доступ к ней осуществляется с помощью определенных РВВ.

Статическое ОЗУ

Прежде всего, следует сказать, что в микроконтроллерах AVR используется линейная организация памяти. Объем статического ОЗУ составляет 512 байт

В адресном пространстве ОЗУ также расположены все регистры микроконтроллеров, под них отведены младшие 96 адресов. Остальные адреса отведены под 512ячеек статического ОЗУ

Каждый регистр имеет свой собственный адрес в пространстве памяти данных. Поэтому к ним можно обращаться двумя способами (как к регистрам и как к памяти), несмотря на то что физически эти регистры не являются ячейками ОЗУ. Такое решение является еще одной отличительной особенностью архитектуры AVR, повышаю щей эффективность работы микроконтроллера и его производительность.

. Регистры ввода/вывода

Все регистры ввода/вывода условно можно разделить на две группы — служебные регистры микроконтроллера и регистры, относя щиеся к конкретным периферийным устройствам (в т. ч. регистры портов ввода/вывода).

Во всех микроконтроллерах семейства Mega (как и в микроконтрол лерах остальных семейств) регистры ввода/вывода располагаются в так называемом пространстве ввода/вывода размером 64 байта

К РВВ, расположенным в основном пространстве ввода/вывода, можно напрямую обратиться с помощью команд IN и OUT, выполняющих пересылку данных между одним из 32-х РОН и пространством ввода/вывода. В системе команд имеется также четыре команды поразрядного доступа, использующие в качестве операндов регистры ввода/вывода: команды установки/сброса отдельного бита (SBI и CBI) и команды проверки состояния отдельного бита (SBIS и SBIC). К сожалению, эти команды могут обращаться только к 1-й половине основных регистров ввода/вывода (адреса $00...$1F).

Помимо непосредственной адресации (с помощью команд IN и OUT), к РВВ можно обращаться и как к ячейкам ОЗУ с помощью соответствующих команд ST/SD/SDD и LD/LDS/LDD

В первом случае используются адреса РВВ, принадлежащие основному пространству ввода/вывода ($00...$3F). Во втором случае адрес РВВ необходимо увеличить на $20.

Среди всех РВВ есть один регистр, используемый наиболее часто в процессе выполнения программ. Этим регистром является регистр состояния SREG. Он располагается по адресу $3F ($5F) и содержит набор флагов, показывающих текущее состояние микроконтроллера. Большинство флагов автоматически устанавливаются в «1» или сбрасываются в «О» при наступлении определенных событий (в соответствии с результатом выполнения команд). Все разряды этого регистра доступны как для чтения, так и для записи; после сброса микроконтроллера все разряды регистра сбрасываются в «О».

Способы адресации памяти данных

Микроконтроллеры поддерживают 8 способов адресации для доступа к различным областям памяти данных (РОН, РВВ,ОЗУ).

Вообще говоря, в действительности способов адресации всего два: прямая адресация и косвенная. Однако каждый способ адресации имеет несколько разновидностей в зависимости от того, к какой области памяти производится обращение (при прямой адресации) или какие дополнительные действия выполняются над индексным регистром (при косвенной адресации).

Прямая адресация

При прямой адресации адреса операндов содержатся непосредственно в слове команды. В соответствии со структурой памяти данных существуют следующие разновидности прямой адресации: прямая адресация одного РОН, прямая адресация двух РОН, прямая адресация РВВ, прямая адресация ОЗУ.

Косвенная адресация

При использовании команд косвенной адресации с постинкрементом после обращения по адресу, который находится в индексном регистре, содержимое индексного регистра увеличивается на 1.

Адресация ОЗУ

Микроконтроллеры семейства поддерживают 6 команд (по 2 для каждого индексного регистра) косвенной адресации с постинкрементом: LD Rd, X+/Y+/Z+ (пересылка байта из ОЗУ в РОН) и ST X+/Y+/Z+, Rd (пересылка байта из РОН в ОЗУ). Адрес регистра общего назначения содержится в разрядах 8... 4 слова команды.

Энергонезависимая память данных (EEPROM)

Все микроконтроллеры семейства Mega имеют в своем составе энергонезависимую память (EEPROM-память). Объем этой памяти 512 байт. EEPROM-память расположена в своем адресном пространстве и так же, как и ОЗУ, организована линейно. Для работы с EEPROM-памятью используются три регистра ввода/вывода: регистр адреса, регистр данных и регистр управления.

Регистр адреса

Регистр адреса EEPROM-памяти EEAR (EEPROM Address Register) физически размещается в двух РВВ EEARH:EEARL, расположенных по адресам $1F (S3F) и $1Е ($ЗЕ) соответственно. В этот регистр загружается адрес ячейки, к которой будет производиться обращение. Регистр адреса доступен как для записи, так и для чтения. При этом в регистре EEARH задействуются только младшие разряды (количество задействованных разрядов зависит от объема EEPROM-памяти). Незадействованные разряды регистра EEARH доступны только для чтения и содержат «О».

Регистр данных

Регистр данных EEPROM-памяти EEDR (EEPROM Data Register) расположен по адресу $1D ($3D). При записи в этот регистр загружаются данные которые должны быть загружены в EEPROM. При чтении помещаются данные считанные из EEPROM.

Регистр управления

Регистр управления EEPROM-памяти EECR (EEPROM control Register) расположен по адресу $1С ($3C). Этот регистр используется для управления доступом к EEPROM-памяти

Прерывания

Общие сведения

Прерывание прекращает нормальный ход программы для выполнения приоритетной задачи, определяемой внутренним или внешним событие» микроконтроллера. При возникновении прерывания микроконтроллер сохраняет в стеке содержимое счетчика команд PC и загружает в него адрес соответствующего вектора прерывания. По этому адресу, как правило, находится команда безусловного перехода к подпрограмме обработки прерывания. Последней командой подпрограммы обработки прерывания должна быть команда RETI, которая обеспечивает возврат в основную программу и восстановление предварительно сохраненного счетчика команд.

Поскольку источниками прерываний, в частности, являются различные периферийные устройства микроконтроллеров, количество прерываний зависит от конкретной модели.

Таблица векторов прерываний

Как и все микроконтроллеры AVR, микроконтроллеры семейства Mega имеют многоуровневую систему приоритетных прерываний. Младшие адреса памяти программ начиная с адреса $0001 отведены под таблицу векторов прерывания. Каждому прерыванию соответствует адрес в этой таблице, который загружается в счетчик команд при возникновении прерывания. Положение вектора в таблице также определяет и приоритет соответствующего прерывания: чем меньше адрес, тем выше приоритет прерывания. Размер вектора прерывания зависит от объема памяти программ микроконтроллера и составляет 1 байт. Соответственно для перехода к подпрограммам обработки прерываний используются команды RJMP.

Таблица может располагаться не только и начале памяти программ, а также и в начале области загрузчика. Причем перемещение таблицы может быть осуществлено непосредственно в ходе выполнения программы.

Управление размещением таблицы прерываний осуществляется двумя младшими разрядами регистров GICR: IVSEL (1-й разряд) и IVSE (0-й разряд). Состояние флага IVSEL определяет положение таблицы в памяти программ. Если флаг сброшен в «О», таблица векторов прерываний располагается в начале памяти программ, если флаг установлен в «1» — в начале области загрузчика. Конкретное значение начального адреса области загрузчика зависит от установок конфигурационных ячеек BOOTSZ1 и BOOTSZO. Разряд IVСЕ предназначен для разрешения изменения флага IVSEL.

Для изменения положения таблицы векторов прерываний необходимо установить разряд IVСЕ в «1» и затем в течение следующих четырех машинных циклов занести требуемое значение в разряд IVSEL. При этом разряд IVCE сбрасывается в «О». В противном случае разряд IVСЕ будет сброшен аппаратно по истечении четырех машинных циклов, запрещая дальнейшее изменение флага IVSEL.

На время выполнения описанной последовательности прерывания автоматически запрещаются и разрешаются только после сброса флага IVCE. Состояние флага I регистра SREG при этом не меняется. Если прерывания в работе микроконтроллера не предусматриваются, то на месте таблицы векторов прерываний может быть размещена часть основной программы

Счетчик команд и выполнение программы

Счетчик команд

Счетчик команд представляет собой регистр, в котором содержится адрес следующей исполняемой команды. Напрямую из программы он недоступен. Размер счетчика команд зависит от объема имеющейся памяти программ и составляет 12 разрядов.

При нормальном выполнении программы содержимое счетчика команд автоматически увеличивается на 1 или на 2 (в зависимости от выполняемой команды) в каждом машинном цикле. Этот порядок нарушается при выполнении команд перехода, вызова и возврата из подпрограмм, а также при возникновении прерываний.

После включения питания, а также после сброса микроконтроллера в счетчик программ автоматически загружается стартовый адрес $0000 или начальный адрес сектора загрузчика. Как правило, по этому адресу располагается команда безусловного перехода к инициализационной части программы.

При возникновении прерывания в счетчик команд загружается адрес соответствующего вектора прерывания. Если прерывания используются в программе, по адресам векторов прерываний должны размещаться команды перехода к подпрограммам обработки прерываний.

Как и во всех микроконтроллерах AVR, в микроконтроллерах семейства Mega используется конвейерная обработка команд.

Абсолютный вызов подпрограммы — команда CALL

При выполнении команды после сохранения в стеке текущего значения счетчика команд в последний загружается число, являющееся операндом команды. С помощью этой команды можно осуществлять вызов в пределах всего адресного пространства имеющихся на сегодняшний день микроконтроллеров AVR.

Команда абсолютного вызова подпрограмм выполняется за 4 машинных цикла.

Косвенный вызов подпрограммы — команда ICALL

Команда ICALL сначала сохраняет в стеке значение счетчика команд. Затем в счетчик команд загружается содержимое индексного регистра. Максимально возможная величина перехода составляет 64К слов (128 Кбайт), поэтому данная команда также не имеет ограничений по области действия.

Как и команда RCALL, команда косвенного вызова подпрограмм выполняется за 3 машинных цикла.

Команды возврата из подпрограмм

В конце каждой подпрограммы обязательно должна находиться команда возврата из нее. В системе команд микроконтроллеров семейства имеется две таких команды. Для возврата из обычной подпрограммы, вызываемой командой RCALL, используется команда RET. Для возврата из подпрограммы обработки прерывания используется команда RETI.

Обе команды восстанавливают из стека содержимое счетчика команд, сохраненное там перед переходом к подпрограмме. Команда возврата из подпрограммы RETI дополнительно устанавливает в «1» флаг общего разрешения прерываний I регистра SREG, сбрасываемый аппаратно при возникновении прерывания.

На выполнение каждой из команд возврата из подпрограммы требуется 4 машинных цикла.

Стек

Во всех микроконтроллерах семейства стек реализован программно. Он размещается в памяти данных, и его глубина определяется только размером свободной области памяти программ. В качестве указателя стека во всех моделях используется пара регистров ввода/вывода SPH:SPL, расположенных по адресам $ЗЕ ($5Е) и $3D ($5D) соответственно. Так как после подачи напряжения питания (или после сброса) в регистрах содержится нулевое значение, в самом начале программы указатель стека необходимо проинициализировать, записав в него значение верхнего адреса памяти данных.

При вызове подпрограмм адрес команды, расположенной за командой вызова, сохраняется в стеке. Значение указателя стека при этом уменьшается на 2, т. к. для хранения счетчика команд требуется 2 байта. При возврате из подпрограммы этот адрес извлекается из стека и загружается в счетчик команд. Значение указателя стека соответственно увеличивается на 2. То же происходит и во время прерывания. При генерации прерывания адрес следующей команды сохраняется в стеке, а при возврате из подпрограммы обработки прерывания он восстанавливается из стека.

Во всех моделях микроконтроллеров семейства стек доступен программно. Для работы со стеком в наборе команд имеется две команды: команда занесения в стек (PUSH) и команда извлечения из стека (POP).

Порты ввода/вывода

Общие сведения

Каждый порт микроконтроллеров состоит из определенного числа выводов, через которые микроконтроллер может осуществлять прием и передачу цифровых сигналов. Задание направления передачи данных через любой контакт ввода/вывода может быть произведено программно в любой момент времени.

Выходные буферы всех портов, имея симметричные нагрузочные характеристики, обеспечивают высокую нагрузочную способность при любом уровне сигнала. Нагрузочной способности достаточно для непосредственного управления светодиодными индикаторами.

Входные буферы всех выводов построены по схеме триггера Шмитта. Для всех входов имеется возможность подключения внутреннего подтягивающего резистора между входом и шиной питания.

Отличительной особенностью портов микроконтроллеров семейства Mega (как и всех микроконтроллеров AYR) при использовании их в качестве цифровых портов ввода/вывода общего назначения является реализация истинной функциональности вида «чтение/модификация/запись». Благодаря этому можно выполнять операции над любым выводом (с помощью команд SBI и CBI), не влияя на другие выводы порта. Это относится к изменению режима работы контакта ввода/вывода, к изменению состояния выходного буфера (для выходов) и к изменению состояния внутреннего подтягивающего резистора (для входов).

Регистры портов ввода/вывода

Обращение к портам производится через регистры ввода/вывода. Под каждый порт в адресном пространстве ввода/вывода зарезервировано по 3 адреса, по которым размещены следующие регистры: регистр данных порта PORTx, регистр направления данных DDRx и регистр выводов порта PINx. Действительные названия регистров получаются подстановкой названия порта вместо символа «х», соответственно регистры порта А называются PORTA, DDRA, PINA, порта В — PORTB, DDRB, PINB и т. д. Поскольку с помощью регистров PIN* осуществляется доступ к физическим значениям сигналов на выводах порта, они доступны только для чтения, тогда как остальные два регистра доступны и для чтения, и для записи.

Таймеры

Таймер/счетчик ТО имеет минимальный набор функций. Он может использоваться только для отсчета и измерения временных интервалов или как счетчик внешних событий, возможность генерации сигналов с широтно-импульсной модуляцией (ШИМ) фиксированной разрядности, а также возможность работать в асинхронном режиме в качестве часов реального времени.

Таймер/счетчик Т2 полностью аналогичен таймеру/счетчику ТО

Таймер/счетчик ТЗ имеет те же функциональные возможности, что и ТО, он может работать в качестве широтно-импульсного модулятора, но уже переменной разрядности и к тому же многоканальный.

Сторожевой таймер

Как и микроконтроллеры остальных семейств, все микроконтроллеры семейства Mega имеют в своем составе сторожевой таймер, предназначенный для защиты микроконтроллера от сбоев в процессе работы. Исполнение сторожевого таймера одинаково для всех моделей семейства.

Сторожевой таймер имеет независимый тактовый генератор, поэтому он работает даже во время нахождения микроконтроллера в любом из спящих режимов. Типовое значение частоты этого генератора равно 1 МГц при Vcс=5.0В. Фактическая частота генератора зависит oт напряжения питания устройства, температуры, технологического разброса.

Если сторожевой таймер включен, то через промежутки времени равные его периоду, он выполняет сброс микроконтроллера. Чтобы избежать сброса при нормальном выполнении программы, сторожевой таймер необходимо регулярно сбрасывать через промежутки времени, меньшие его периода. Сброс сторожевого таймера осуществляется командой WDR.

Для управления сторожевым таймером предназначен регистр WDTCR, который во всех моделях расположен по адресу $21 ($41).

Назначение выводов таймеров/счетчиков

Каждый таймер/счетчик использует один или более выводов микроконтроллера. Эти выводы линии портов ввода/вывода общего назначения, а функции, реализуемые этими выводами при работе совместно с таймерами/счетчиками, являются их альтернативными функциями.

Аналоговый компаратор

Модуль аналогового компаратора входит в состав всех без исключения микроконтроллеров семейства Mega. Будучи включенным, компаратор позволяет сравнивать значения напряжений, присутствующих на двух выводах микроконтроллера. Результатом сравнения является логическое значение, которое может быть прочитано из программы. По результату сравнения может быть сгенерировано прерывание, а также осуществлен захват состояния таймера/счетчика Т1. Последняя функция позволяет, в частности, измерять длительности аналоговых сигналов.

Используемые компаратором выводы являются контактами портов ввода/вывода общего назначения

Чтобы указанные выводы могли использоваться аналоговым компаратором, они должны быть сконфигурированы как входы (соответствующий разряд регистра DDRx установлен в «1»). Кроме того, необходимо отключить внутренние подтягивающие резисторы записью лог. 0 в соответствующий разряд регистра PORTх.

Аналого-цифровой преобразователь

Модуль 10-разрядного АЦП последовательного приближения входящий в состав моделей имеет следующие основные параметры:

• абсолютная погрешность: ±2 МЗР;

• интегральная нелинейность: ±0.5 МЗР;

• быстродействие: до 15 тыс. выборок/с.

На входе модуля АЦП всех моделей имеется 8-канальный аналоговый мультиплексор, предоставляющий в распоряжение пользователя 8 каналов с несимметричными входами.

В качестве источника опорного напряжения для АЦП может использоваться как напряжение питания микроконтроллера, так и внутренний либо внешний источник опорного напряжения.

В процессе работы АЦП может функционировать в двух режимах:

• режим одиночного преобразования, когда запуск каждого преобразования инициируется пользователем;

• режим непрерывного преобразования, когда запуск преобразований выполняется непрерывно через определенные интервалы времени.

Универсальный асинхронный (синхронный/асинхронный) приемопередатчик

Все без исключения микроконтроллеры семейства Mega имеют в своем составе модули либо универсального асинхронного (UART), либо универсального синхронно/асинхронного (USART) приемопередатчика. Более того, в некоторых моделях имеется по два таких модуля. Заметим, что модули USART при работе в асинхронном режиме совместимы с модулями UART как по расположению разрядов управляющих регистров, так и по функционированию. Небольшие различия имеются только в работе схемы буферизации блока приемника модулей и в названии (но не в назначении) некоторых разрядов управляющих регистров.

Все модули приемопередатчиков обеспечивают полнодуплексный обмен по последовательному каналу, при этом скорость передачи данных может варьироваться в довольно широких пределах. В модулях UART посылка может быть 8- или 9-разрядной, а в модулях USART ее длина может составлять от 5 до 9 разрядов. Еще одной особенностью модулей USART является наличие схем формирования и контроля четности.

Модули USART/UART, реализованные в микроконтроллерах семейства, могут обнаруживать следующие внештатные ситуации:

• переполнение;

• ошибка кадрирования;

• неверный старт-бит.

Для уменьшения вероятности сбоев в модулях также реализована такая полезная функция, как фильтрация помех.

Для взаимодействия с программой в модулях предусмотрены 3 прерывания, запрос на генерацию которых формируется при наступлении следующих событий: «передача завершена», «регистр данных передатчика пуст» и «прием завершен».

Как обычно, выводы микроконтроллера, используемые модулями USART/UART, являются линиями портов ввода/вывода общего назначения.

Последовательный периферийный интерфейс SPI

Последовательный периферийный интерфейс SPI (Serial Peripheral In-lerface), имеет двоякое назначение. Во-первых, с его помощью может осуществляться обмен данными между микроконтроллером и различными периферийными устройствами, такими, как цифровые потенциометры, ЦАП/АЦП, FLASH-ПЗУ и др. Посредством этого интерфейса также может производиться обмен данными между несколькими микроконтроллерами AVR. Кроме того, через интерфейс SPI может быть осуществлено программирование микроконтроллера (т. е. режим последовательного программирования). При обмене данными по интерфейсу SPI микроконтроллер AVR может работать как ведущий (режим «Master») либо как ведомый (режим «Slave»). При этом пользователь может задавать скорость передачи (семь программируемых значений) и формат передачи (от младшего разряда к старшему или наоборот).

Дополнительной возможностью подсистемы SPI является «пробуждение» микроконтроллера из режима Idle при поступлении данных.

Модуль SPI использует четыре вывода микроконтроллера. Как и для большинства прочих периферийных устройств, эти выводы являются линиями портов ввода/вывода общего назначения.

Последовательный двухпроводный интерфейс

Модуль двухпроводного последовательного интерфейса (Two-wire Serial Interface, TWI) является полным аналогом базовой версии интерфейса 12С фирмы «Philips». Интерфейс TWI позволяет объединить вместе до 128 различных устройств с помощью двунаправленной шины, состоящей всего из двух линий: линии тактового сигнала (SCL) и линии данных (SDA). Единственными дополнительными элементами для реализации шины являются два подтягивающих резистора, по одному на каждую линию.

Шинные формирователи всех TWI-совместимых устройств выполняются по схеме с открытым коллектором (стоком), что позволяет реализовать функцию «монтажное И». Соответственно, НИЗКИЙ уровень на линии устанавливается тогда, когда одно или более устройств выставляют на линию сигнала лог. 0, а ВЫСОКИЙ уровень на линии устанавливается тогда, когда все устройства, подключенные к ней, устанавливают свои выходы в третье состояние.

Общие сведения о системе команд

Введение в систему команд

Система команд микроконтроллеров весьма развита и насчитывает до 130 различных инструкций. Несмотря на то что микроконтроллеры AVR являются микроконтроллерами с RISC-архитектурой (процессор с сокращенным набором команд), по количеству реализованных инструкций и их разнообразию они больше похожи на микроконтроллеры с CISC-архитектурой (процессор с полным набором команд). Практически каждая из команд (за исключением команд, у которых одним из операндов является 16-разрядный адрес) занимает только одну ячейку памяти программ. Причем это достигнуто не за счет сокращения количества команд процессора, а за счет увеличения разрядности памяти программ.

Операнды

Программа для любого микроконтроллера представляет собой последовательность команд, записанных в памяти программ. Большинство команд при выполнении изменяют содержимое одного или нескольких регистров общего назначения, регистров ввода/вывода или ячеек ОЗУ.

Для обращения к различным областям адресного пространства памяти данных используются различные команды, реализующие, в свою очередь, различные способы адресации

Доступ к регистрам ввода/вывода осуществляется по их адресам, являющимися операндами команды. Вместе с тем при написании ассемблерных программ гораздо удобнее обращаться к регистрам, используя вместо числовых значений адресов их стандартные, принятые символические имена.

Чтобы задать соответствие этих имен реальным адресам необходимо подключить в начале программы (при помощи директивы ассемблера .INCLUDE) файл определения адресов регистров ввода/вывода. Помимо всего прочего, такое решение облегчит перенос программного обеспечения с одного типа кристалла на другой.

Эти файлы (для каждой модели микроконтроллеров семейства) свободно распространяются фирмой «Atmel» вместе с документацией на микроконтроллеры (в частности, они, находятся на web-сайте фирмы). Для РОН, входящих в состав индексных регистров, в этих файлах определяются также дополнительные символические имена

Дополнительные символические имена индексных регистров

| Регистр | Символическое имя |

| R26 | XL |

| R27 | ХН |

| R28 | YL |

| R29 | YH |

| R30 | ZL |

| R31 | ZH |

Названия этих файлов унифицированы и определяются следующим образом:

<номер модели>def. inc

Например, программа для микроконтроллера ATtinyl5L должна содержать следующую директиву ассемблера:

.include "tnl5def.inc"

а для микроконтроллера ATmega8535:

.include "m8535def.inc"

Необходимо только помнить, что если для обращения к регистру ввода/вывода используются команды обмена с ОЗУ, то к символическому имени требуется прибавить число $20.

Как уже было упомянуто, в микроконтроллерах память программ является 16-разрядной. Соответственно большинство команд описываются 16-разрядным словом, которое называется также кодом операции (КОП). Код операции — это число, расположенное в памяти программ и определяющее действие, которое необходимо произвести между источником и приемником. Некоторые команды, у которых один из операндов является 16-разрядным адресом, занимают две ячейки памяти программ. Соответственно, код операции таких команд является 4-байтным числом.

В ряде случаев значение операнда-источника может содержаться непосредственно в коде операции, а не в регистре. Это происходит в том случае, когда операндом-источником является константа.

Типы команд

Все множество команд микроконтроллеров можно разбить на несколько групп:

• команды логических операций;

• команды арифметических операций и команды сдвига;

• команды операций с битами;

• команды пересылки данных;

• команды передачи управления;

• команды управления системой.

Далее подробно описана каждая группа команд.

Команды логических операций

Команды логических операций позволяют выполнять стандартные логические операции над байтами, такие, как логическое умножение (И), логическое сложение (ИЛИ), операцию «исключающее ИЛИ», а также вычисление обратного (дополнение до единицы) и дополнительного (дополнение до двух) кодов числа. К этой группе можно отнести также команды очистки/установки регистров и команду перестановки тетрад. Операции производятся между регистрами общего назначения либо между регистром и константой; результат сохраняется в РОН. Все команды из этой группы выполняются за один машинный цикл.

Команды арифметических операций и команды сдвига

К данной группе относятся команды, позволяющие выполнять такие базовые операции, как сложение, вычитание, сдвиг (вправо и влево), инкремент и декремент. В микроконтроллерах семейства Mega также имеются команды, позволяющие осуществлять умножение 8-разрядных значений. Все операции производятся только над регистрами общего назначения. При этом микроконтроллеры AVR позволяют легко оперировать как знаковыми, так и без знаковыми числами, а также работать с числами, представленными в дополнительном коде.

Почти все команды рассматриваемой группы выполняются за один машинный цикл. Команды умножения и команды, оперирующие двухбайтовыми значениями, выполняются за два цикла.

Команды операций с битами

К данной группе относятся команды, выполняющие установку или сброс заданного разряда РОН или РВВ. Причем для изменения разрядов регистра состояния SREG имеются также дополнительные команды (точнее говоря, эквивалентные мнемонические обозначения общих команд), т. к. проверка состояния разрядов именно этого регистра производится чаще всего. Условно к этой группе можно отнести также две команды передачи управления типа «проверка/пропуск», которые пропускают следующую команду в зависимости от состояния разряда РОН или РВВ.

Все задействованные разряды РВВ имеют свои символические имена. Определения этих имен описаны в том же включаемом файле, что и определения символических имен адресов регистров. Таким образом, после включения в программу указанного файла в командах вместо числовых значений номеров разрядов можно будет указывать их символические имена.

Всем командам данной группы требуется один машинный цикл для выполнения, за исключением случаев, когда в результате проверки происходит пропуск команды. В этом случае команда выполняется за 2 или 3 машинных цикла в зависимости от пропускаемой команды.

Команды пересылки данных

Команды этой группы предназначены для пересылки содержимого ячеек, находящихся в адресном пространстве памяти данных. Разделение адресного пространства на три части (РОН, РВВ, ОЗУ) предопределило разнообразие команд данной группы. Пересылка данных, выполняемая командами группы, может производиться в следующих направлениях:

• РОН <=> РОН;

• РОН <=> РВВ;

• РОН <=> память данных.

Также к данной группе можно отнести стековые команды PUSH и POP, позволяющие сохранять в стеке и восстанавливать из стека содержимое РОН.

На выполнение команд данной группы, требуется в зависимости от команды от одного до трех машинных циклов.

Команды передачи управления

В эту группу входят команды перехода, вызова подпрограмм и возврата из них и команды типа «проверка/пропуск», пропускающие следующую за ними команду при выполнении некоторого условия. Также к этой группе относятся команды сравнения, формирующие флаги регистра SREG и предназначенные, как правило, для работы совместно с командами условного перехода.

В системе команд микроконтроллеров семейства имеются команды как безусловного, так и условного переходов. Команды относительного перехода (RJMP), а в микроконтроллерах семейства Mega также косвенного (IJMP) и абсолютного (JMP) безусловного перехода являются самыми простыми в этой группе. Их функция заключается только в записи нового адреса в счетчик команд. Команды условного перехода также изменяют содержимое счетчика команд, однако это изменение происходит только при выполнении некоторого условия или, точнее, при определенном состоянии различных флагов регистра SREG.

Все команды условного перехода можно разбить на две подгруппы. Первая подгруппа команды условного перехода общего назначения. В эту подгруппу входят две команды BRBS s,k HBRBC s,k, в которых явно задается номер тестируемого флага регистра SREG. Соответственно, переход осуществляется при SREG.s = 0 (brbc) или SREG.S = I (brbs). Другую подгруппу составляют 18 специализированных команд, каждая из которых выполняет переход по какому-либо конкретному условию («равно», «больше или равно», «был перенос» и т. п.). Причем одни команды используются после сравнения без знаковых чисел, другие после сравнения чисел со знаком. Возможные проверяемые условия, а также соответствующие им команды условного перехода приведены в таблице.

Сводная таблица команд условного перехода

| Проверка | Логическое условие | Команда | Обратная проверка | Логическое условие | Команда | Тип данных |

| Rd>Rr | Z»(N©V) = 0 | BRLT* | Rd<Rr | Z + (N®V)=1 | BRGE* | Co знаком |

| Rd>Rr | (NeV) = 0 | BRGE | Rd<Rr | (N©V) = 1 | BRLT | Co знаком |

| Rd = Rr | Z=l | BREQ | Rd^Rr | Z = 0 | BRNE | Co знаком |

| Rd<Rr | Z + (N®V) = 1 | BRGE* | Rd>Rr | Z»(N©V) = 0 | BRLT* | Co знаком |

| Rd<Rr | (N®V)=1 | BRLT | Rd>Rr | (N®V) = 0 | BRGE | Co знаком |

| Rd>Rr | C + Z = 0 | BRLO* | Rd<Rr | C + Z=l | BRSH* | Без знака |

| Rd>Rr | C = 0 | BRHS/ BRCC | Rd<Rr | C=l | BRLO/ BRCS | Без знака |

| Rd = Rr | z-\ | BREQ | Rd*Rr | z = o | BRNE | Без знака |

| Rd<Rr | C = Z=1 | BRSH * | Rd>Rr | c = z = o | BRLO* | Без знака |

| Rd<Rr | C=l | BRLO/ BRCS | Rd>Rr | c=o | BRSH/ BRCC | Без знака |

| «Перенос» | C = l | BRCS | «Нет переноса» | c = o | BRCC | |

| «Меньше нуля» | N = 1 | BRMI | «Больше нуля» | N = 0 | BRPL | |

| «Переполнение» | V=l | BRVS | «Нет переполнения» | V=0 | BRVC | |

| «Ноль» | Z=l | BREQ | «Не ноль» | z=o | BRNE | |

| * Для перехода по этому условию операнды предшествующей команды сравнения должны быть записаны в обратном порядке, т. е. вместо СР Rd.Rr—>CP Rr.Rd. | ||||||

Вообще говоря, команды, указанные в таблице, являются всего лишь эквивалентными мнемоническими обозначениями команд BRBS s, к и BRBC s , к с определенными значениями операнда «s». Команда BREQ имеет, например, такой же код операции, что и команда BRBS 1,к, а команда BRGE k - BRBC 4,к.

Команды вызова подпрограммы (icall, rcall, call) работают практически так же, как и команды безусловного перехода. Отличие заключается в том, что, перед тем как выполнить переход, значение счетчика команд сохраняется в стеке. Кроме того, подпрограмма должна заканчиваться командой возврата RET.

Очевидно, что команды передачи управления нарушают нормальное (линейное) выполнение основной программы. Каждый раз, когда выполняется команда из этой группы (кроме команд сравнения), нормальное функционирование конвейера нарушается. Перед загрузкой в конвейер нового адреса производится остановка и очистка выполняемой последовательности команд. Соответственно, реинициализация конвейера приводит к необходимости использования нескольких машинных циклов для выполнения таких команд.

Команды управления системой

В эту группу входят всего 3 команды:

• NOP — пустая команда;

• SLEEP — перевод микроконтроллера в режим пониженного энергопотребления;

• wdr — сброс сторожевого таймера.

Все команды этой группы выполняются за один машинный цикл.

Сводные таблицы команд

В Таблице указаны все команды, которыми располагают микроконтроллеры. В каждой таблице команды сгруппированы по функциональному признаку. В таблицах приведены такие основные сведения о командах, как мнемоническое обозначение команды, ее описание, число машинных циклов, необходимых для ее выполнения, а также флаги регистра SREG, на которые воздействует эта команда.

Группа команд логических операций

| Мнемоника | Описание | Операция | Циклы | Флаги |

| AND Rd, Rr | «Логическое И» двух РОН | Rd = Rd • Rr | 1 | Z,N,V |

| ANDI Rd, K | «Логическое И» РОН и константы | Rd = Rd • К | 1 | Z,N,V |

| EOR Rd, Rr | «Исключающее ИЛИ» двух РОН | Rd = Rd ® Rr | 1 | Z,N,V |

| OR Rd, Rr | «Логическое ИЛИ» двух РОН | Rd = Rd v Rr | 1 | Z,N,V |

| ORI Rd, K | «Логическое ИЛИ» РОН и константы | Rd = Rd v К | 1 | Z,N,V |

| COM Rd | Перевод в обратный код | Rd = $FF-Rd | 1 | Z,C,N,V |

| NEG Rd | Перевод в дополнительный код | Rd = $00-Rd | 1 | Z,C,N,V,H |

| CLR Rd | Сброс всех разрядов РОН | Rd = Rd ® Rd | 1 | Z,N,V |

| SER Rd | Установка всех разрядов РОН | Rd = $FF | 1 | |

| TST Rd | Проверка РОН на отрицательное или нулевое значение | Rd • Rd | 1 | Z,N,V |

| SWAP Rd | Обмен местами тетрад в РОН |

Rd(3...O) = Rd(7...4), Rd(7...4) = Rd(3...O) |

1 |

Группа команд арифметических операций

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| ADD Rd. Rr | Сложение двух РОН | Rd = Rd + Rr | 1 | Z,C,N,V,H | |||||||||

| ADC Rd. Rr | Сложение двух РОН с переносом | Rd = Rd + Rr + C | 1 | Z,C,N,V,H | |||||||||

| ADIW Rd, K | Сложение регистровой пары с константой | Rdh:RdI = Rdh:Rdl + К | 2 | Z,C,N,V,S | |||||||||

| SUB Rd, Rr | Вычитание двух РОН | Rd = Rd-Rr | 1 | Z,C,N,V,H | |||||||||

| SUBI Rd, K | Вычитание константы из РОН | Rd = Rd-K | 1 | Z,C,N,V,H | |||||||||

| SBC Rd, Rr | Вычитание двух РОН с заемом | Rd=Rd-Rr-C | 1 | Z,C,N,V,H | |||||||||

| SBCI Rd, K | Вычитание константы из РОН с заемом | Rd = Rd-K-C | 1 | Z,C,N,V,H | |||||||||

| SBIW Rd, K | Вычитание константы из регистровой пары | Rdh:Rdl = Rdh:Rdt-K | 2 | Z,C,N,V,S | |||||||||

| DEC Rd | Декремент РОН | Rd = Rd-l | 1 | Z,N,V | |||||||||

| INC Rd | Инкремент РОН | Rd = Rd + 1 | 1 | Z,N,V | |||||||||

| ASR Rd | Арифметический сдвиг вправо | Rd(n) = Rd(n+ 1), n = 0...6 | 1 | Z,C,N,V | |||||||||

| LSL Rd | Логический сдвиг влево | Rd(n+l) = Rd(n), Rd(0) = 0 | 1 | Z,C,N,V | |||||||||

| LSR Rd | Логический сдвиг вправо | Rd(n) = Rd(n+l),Rd(7) = 0 | 1 | Z,C,N,V | |||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| ROL Rd | Сдвиг влево через перенос | Rd(0) = C, Rd(n+l) = Rd(n), С = Rd(7) | 1 | Z,C,N,V | |||||||||

| ROR Rd | Сдвиг вправо через перенос | Rd(7) = C, Rd(n) = Rd(n+l), С = Rd(0) | 1 | Z,C,N,V | |||||||||

| MUL Rd, Rr | Умножение беззнаковых чисел | Rl:RO = RdXRr | 2 | Z,C | |||||||||

| MULS Rd, Rr | Умножение чисел со знаком | Rl:RO = RdXRr | 2 | Z,C | |||||||||

|

MULSU Rd, Rr |

Умножение беззнакового числа на число со знаком | Rl:RO = RdXRr | 2 | Z,C | |||||||||

| FMDL Rd, Rr | Умножение дробных беззнаковых чисел | Rl:RO = (RdXRr)«l | 2 | Z,C | |||||||||

|

FMULS Rd, Rr |

Умножение дробных чисел со знаком | Rl:RO = (RdXRr)«l | 2 | Z,C | |||||||||

|

FMULSU Rd, Rr |

Умножение дробного беззнакового числа и дробного числа со знаком | Rl:RO = (RdXRr)«1 | 2 | Z,C | |||||||||

| Группа команд операций с битами | |||||||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги |

|

||||||||

| CBR Rd, K | Сброс разряда(ов) РОН | Rd = Rd»($FF-K) | 1 | Z,N,V |

|

||||||||

| SBR Rd, K | Установка разрада(ов) РОН | Rd=RdvK | 1 | Z, N,V |

|

||||||||

| CBI A, b | Сброс разряда РВВ | A.b = 0 | 2 |

|

|||||||||

| SBI A, b | Установка разряда РВВ | A.b=l | 2 |

|

|||||||||

| BCLR s | Зброс флага | SREG.S - 0 | 1 | SREG.S |

|

||||||||

| BSET s | Установка флага | SREG.S=l | 1 | SREG.S |

|

||||||||

| BLD Rd, b | Загрузка разряда РОН из флага Т (SREG) | Rd.b = T | 1 |

|

|||||||||

| BST Rr, b | Запись разряда РОН в флаг Т (SREG) | T = Rr.b | 1 | T |

|

||||||||

| CLC | Сброс флага переноса | С = 0 | 1 | С |

|

||||||||

| SEC | Установка флага переноса | C = l | 1 | С |

|

||||||||

| CLN | Сброс флага отр. числа | N = 0 | 1 | N |

|

||||||||

| SEN | Установка флага отр. числа | N = 1 | 1 | N |

|

||||||||

| CLZ | Сброс флага нуля | Z = 0 | 1 | Z |

|

||||||||

| SEZ | Установка флага нуля | Z = l | 1 | Z |

|

||||||||

| CLI | Общее запрещение прерываний | 1 = 0 | 1 | I |

|

||||||||

| SEI | Общее разрешение прерываний | 1 = 1 | 1 | I |

|

||||||||

| CLS | Сброс флага знака | S = 0 | 1 | S |

|

||||||||

| SES | Установка флага знака | S = l | 1 | S |

|

||||||||

| CLV | Сброс флага переполнения доп. кода | V = 0 | 1 | V |

|

||||||||

| SEV | Установка флага переполнения доп. кода | V = l | 1 | V |

|

||||||||

| CLT | Сброс флага Т | T = 0 | 1 | T |

|

||||||||

| SET | Установка флага Т | T = l | 1 | T |

|

||||||||

| CLH | Сброс флага половинного переноса | H = 0 | 1 | H |

|

||||||||

| SEH | Установка флага половинного переноса | H = l | 1 | H |

|

||||||||

| Группа команд пересылки данных | |||||||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| MOV Rd, Rr | Пересылка между РОН | Rd = Rr | 1 | ||||||||||

|

MOVW Rd, Rr |

Пересылка двухбайтовых значений | Rd + l:Rd = Rr+l:Rr | 1 | ||||||||||

| LDI Rd, K | Загрузка константы в РОН | Rd = K | 1 | ||||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| LD Rd, X | Косвенное чтение | Rd=[X] | 2 | ||||||||||

| LD Rd, X+ | Косвенное чтение с постинкрементом | Rd = [X],X = X+I | 2 | ||||||||||

| LD Rd,-X |

Косвенное чтение с преддекрементом |

X = X-l,Rd = [X] | 2 | ||||||||||

| LD Rd, Y | Косвенное чтение | Rd=[Y] | 2 | ||||||||||

| LD Rd, Y+ | Косвенное чтение с постинкрементом | Rd = [Y],Y = Y+l | 2 | ||||||||||

| LD Rd,-Y | Косвенное чтение с преддекрементом | Y=Y-l,Rd=[Y] | 2 | ||||||||||

| LDD Rd, Y+q | Косвенное относительное чтение | Rd = [Y+q] | 2 | ||||||||||

| LD Rd,Z | Косвенное чтение | Rd = [Z] | 2 | ||||||||||

| LD Rd, Z+ | Косвенное чтение с постинкрементом | Rd = [Z],Z = Z+l | 2 | ||||||||||

| LD Rd,-Z | Косвенное чтение с преддекрементом | Z = Z - 1, Rd = [Z] | 2 | ||||||||||

| LDD Rd, Z+q | Косвенное относительное чтение | Rd = [Z + q] | 2 | ||||||||||

| LDS Rd, k | Непосредственное чтение из ОЗУ | Rd = [k] | 2 | ||||||||||

| ST X, Rr | Косвенная запись | [X] = Rr | 2 | ||||||||||

| ST X+, Rr | Косвенная запись с постинкрементом | [X] = Rr, X=X+1 | 2 | ||||||||||

| ST -X, Rr | Косвенная запись с преддекрементом | X = X-l,[X] = Rr | 2 | ||||||||||

| ST Y, Rr | Косвенная запись | [Y] = Rr | 2 | ||||||||||

| ST Y+, Rr | Косвенная запись с постинкрементом | [Y] = Rr, Y=Y+1 | 2 | ||||||||||

| ST –Y, Rr | Косвенная запись с преддекрементом | Y=Y-l,[X] = Rr | 2 | ||||||||||

| STD Y+ q, Rr | Косвенная относительная запись | [Y+q] = Rr | 2 | ||||||||||

| ST Z, Rr | Косвенная запись | [Z] = Rr | 2 | ||||||||||

| ST Z+, Rr | Косвенная запись с постинкрементом | [Z] = Rr,Z = Z+l | 2 | ||||||||||

| ST –Z ,Rr | Косвенная запись с преддекрементом | Z = Z-l,[Z] = Rr | 2 | ||||||||||

| STD Z+ q, Rr | Косвенная относительная запись | [Z + q] = Rr | 2 | ||||||||||

| STS k, Rr | Непосредственная запись в ОЗУ | [k] = Rr | 2 | ||||||||||

| LPM | Загрузка данных из памяти программ | R0 = {Z} | 3 | ||||||||||

| LPM Rd, Z | Загрузка данных из памяти программ | Rb={Z} | 3 | ||||||||||

| LPM Rd, Z+ | Загрузка данных из памяти программ с постинкрементом | Rb = {Z},Z = Z+1 | 3 | ||||||||||

| ELPM | Расширенная загрузка данных из памяти программ | RO = {RAMPZ:Z} | 3 | ||||||||||

| ELPM Rd, Z | Расширенная загрузка данных из памяти программ | Rb={RAMPZ:Z} | 3 | ||||||||||

| ELPM Rd, Z+ | Расширенная загрузка данных из памяти программ с постинкрементом | Rb = {RAMPZ:Z}, RAMPZ:Z = RAMPZ:Z+1 | 3 | ||||||||||

| SPM | Запись в память программ | {Z} = RI:R0 | |||||||||||

| IN Rd, A | Пересьика из РВВ в РОН | Rd = A | 1 | ||||||||||

| OUT A, Rr | Пересылка из РОН в РВВ | A=Rr | 1 | ||||||||||

| PUSH Rr | Сохранение байта в стеке | STACK - Rr | 2 | ||||||||||

| POP Rd | Извлечение байта из стека | Rd = STACK | 2 | ||||||||||

| Группа команд передачи управления | |||||||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| RJMP k | Относительный безусловный переход | РС =РС + к+1 | 2 | ||||||||||

| IJMP | Косвенный безусловный переход | РС =Z | 2 | ||||||||||

| Мнемоника | Описание | Операция | Циклы | Флаги | |||||||||

| JMP к | Абсолютный переход | РС = к | 3 | ||||||||||

| RCALL к | Этносительный вызов подпрограммы | PC = PC + к + 1 | 3 | ||||||||||

| ICALL | Сосвенный вызов подпрограммы | PC = Z | 3 | ||||||||||

| CALL к | Абсолютный вызов подпрограммы | РС = к | 4 | ||||||||||

| RET | Возврат из подпрограммы | PC = STACK | 4 | ||||||||||

| RETI | Возврат из подпрограммы обработки прерывания | PC = STACK | 4 | ||||||||||

| СР Rd, Rr | Сравнение РОН | Rd-Rr | 1 | Z,N,V,C,H | |||||||||

| СРС Rd, Rr | Сравнение РОН с учетом переноса | Rd-Rr-C | 1 | Z,N,V,C,H | |||||||||

| CPI Rd, K | Сравнение РОН с константой | Rd-K | 1 | Z,N,V,C,H | |||||||||

|

CPSE Rd, Rr |

Сравнение и пропуск следующей команды при равенстве | Если Rd = Rr, то PC = PC + 2 (3) | 1/2/3 | ||||||||||

| SBRC Rr, b | Пропуск след. команды, если разряд РОН сброшен | Если Rr.b = 0, то PC = PC + 2 (3) | 1/2/3 | ||||||||||

| SBRS Rr, b | Пропуск след. команды, если разряд РОН установлен | Если Rr.b=l, то PC = PC + 2 (3) | 1/2/3 | ||||||||||

| SBIC A, b | Пропуск след. команды, если разряд РВВ сброшен | Если A.b = 0, то PC = PC + 2 (3) | 1/2/3 | ||||||||||

| SBIS A ,b | Пропуск след. команды, если разряд РВВ установлен | Если А.Ь= 1, то PC = PC + 2 (3) | 1/2/3 | ||||||||||

| BRBC s, k | Переход, если флаг s регистра SREG сброшен | Если SREG.s = 0, то РС = РС + к+1 | 1/2 | ||||||||||

| BRBS s, k | Переход, если флаг s регистра SREG установлен | Если SREG.s =1, то РС = РС + к+1 | 1/2 | ||||||||||

| BRCS к | Переход по переносу | Если С =1, то РС = РС + к+1 | 1/2 | ||||||||||

| BRCC к | Переход, если нет переноса | Если С = 0, то РС = РС + к+1 | 1/2 | ||||||||||

| BREQ к | Переход по «равно» | Если Z = l, то РС = РС + к+1 | 1/2 | ||||||||||

| BRNE к | Переход по «не равно» | Если Z = 0, то РС = РС + к+1 | 1/2 | ||||||||||

| BRSH к | Переход по «выше или равно» | Если С = 0, то РС = РС + к+1 | 1/2 | ||||||||||

| BRLO к | Переход по «меньше» | Если С =1, то РС = РС + к+1 | 1/2 | ||||||||||

| BRMI . | Переход по «отрицательное значение» | Если N = 1, то РС = РС + к + | 1/2 | ||||||||||

| BRPL | Переход по «положительное значение» | Если N = 0, то РС = РС + к+1 | 1/2 | ||||||||||

| BRGE | Переход по «больше или равно» (числа со знаком) | Если (N®V) = 0, то PC = PC + к + 1 | 1/2 | ||||||||||

| BRLT | Переход по «меньше нуля» (числа со знаком) | Если (N®V)=l, то PC = PC + к + 1 | 1/2 | ||||||||||

| BRHS | Переход по половинному переносу | Если Н = 1, то PC = PC + к + 1 | 1/2 | ||||||||||

| BRHC | Переход, если нет половинного переноса | Если Н = 0, то PC = PC + к + 1 | 1/2 | ||||||||||

| BRTS | Переход, если флаг Т установлен | Если Т= 1, то РС = РС + к+1 | 1/2 | ||||||||||

| BRTC | Переход, если флаг Т сброшен | ЕслиТ = 0, тоРС = РС + к+1 | 1/2 | ||||||||||

| BRVS | Переход по переполнению доп. кода | ЕслиУ=1, тоРС = РС + к+1 | 1/2 | ||||||||||

| BRVC | Переход, если нет переполнения доп. кода | ЕслиУ = 0, тоРС = РС + к+1 | 1/2 | ||||||||||

| BRID | Переход, если прерывания запрещены | Если I = 0, тоРС = РС + к+1 | 1/2 | ||||||||||

| BRIE | Переход, если прерывания разрешены | Если1 = 1, тоРС = РС + к+1 | 1/2 | ||||||||||

Группа команд управления системой

| Мнемоника | Описание | Операция | Циклы | Флаги |

| NOP | Нет операции | пустая команда | 1 | |

| SLEEP | Переход в «спящий» режим | перевод микроконтроллера в режим пониженного энергопотребления | 3 | |

| WDR | Сброс сторожевого таймера | сброс сторожевого таймера | 1 |

| Обозначение | Описание | |

| Регистр состояния | ||

| SREG | Регистр состояния микроконтроллера | |

| C | Флаг переноса | |

| Z | Флаг нуля | |

| N | Флаг отрицательного значения | |

| V | Флаг переполнения доп. кода | |

| S | Флаг знака (S=N®V) | |

| H | Флаг половинного переноса | |

| T | Флаг пользователя | |

| I | Флаг общего разрешения прерываний | |

| Регистры и операнды | ||

| Rd | Регистр приемник | |

| Rr | Регистр источник | |

| K | Константа | |

| k | Адрес-коннстанта | |

| b | Номер разряда РОН | |

| s | Номер разряда регистра состояния | |

| X,Y,Z | Регистры указатели | |

| I\O | Регистр ввода-вывода | |

| A | Адрес в пространства ввода-вывода | |

| q | Смещение при относительной косвенной адресации | |

| [ХХ] | Содержимое ячейки памяти данных по адресу ХХ | |

| {ХХ} | Содержимое ячейки памяти программ по адресу ХХ | |

| Операция | ||

| • | Логическое И | |

| v | Логическое ИЛИ | |

| ® | Исключающее ИЛИ | |

| Система | ||

| РС | Счетчик команд | |

| STACK | Текущий уровень стека | |

| SP | Указатель стека | |

| Флаги | ||

| < > | Команда воздействует на флаг | |

| 0 | Флаг сбрасывается командой в «0» | |

| 1 | Флаг устанавливается командой в «1» | |

| Команда не влияет | ||

Обозначение, используемые при описании команд

© 2010 Интернет База Рефератов