Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Контрольная работа: Микропроцессоры: суть и назначение

Контрольная работа: Микропроцессоры: суть и назначение

МИКРОПРОЦЕССОРЫ

МП называется программное устройство обработки данных, выполняемое средствами микроэлектронных технологий в корпусе одной или нескольких больших интегральных схем.

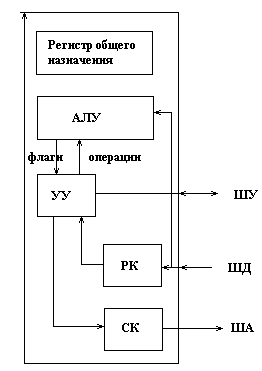

Общая структура МП может быть представлена:

В состав МП входит:

– операционное устройство в виде АЛУ и регистра общего назначения;

– устройство управления (УУ), включающие регистры общего назначения;

– регистр команд (РГ);

– счетчик команд (СК);

СК хранит адрес команды, которую подлежит выполнению. По этому адресу из оперативной памяти извлекается соответствующая команда, занимающая от 1 до нескольких байт и код команды, размещающийся в 1 байте, записывается в РК. В соответствии с кодом команды устройство управления обеспечивает выполнение либо 1 микрооперации, либо микропрограммы, включающей совокупность микроопераций.

В регистре общего назначения размещаются операнды выполняемой операции и промежуточные операции вычисления. Результат выполнения команды может быть размещен либо в регистре общего назначения либо записывается в памяти по сформированному адресу.

В процессе выполнения команды могут быть обращения к памяти за операндами. Архитектура МП определяет множество выполняемых команд, разрядные шины адреса, шины данных, составные шины управления, составных регистров общего и специального назначения, наличием промежуточной буферной памяти. Это КЭШ-память для размещения команд выполнения команды и блоков данных. Возможна модернизация системы команд количеством одновременной обработки бит в операционном устройстве, количеством самих операционных устройств.

Под разрядностью МП понимают количество двоичных разрядов, обрабатываемых операционным устройством МП.

Типичным представителем 8-разрядного МП есть Intel 8080, КР 580.

МП имеет 8-разрядную шину данных и 8-разрядное операционное устройство, 16-разрядную шину адреса. МП, выполненный на основе n-МОП технологий. Питание имеют уровни 12В, ±5В.

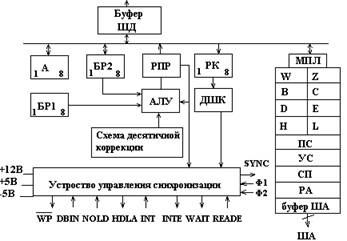

Общая структура МП имеет следующий вид:

Операционное устройство представлено: АЛУ, схемой десятичной коррекции, регистр общего назначения А (аккумулятор), в котором размещается 1 из операндов и после выполнения операции результат выполнения:

2 буферных регистра БР1 и БР2.

Помимо этого в составе регистра общего назначения имеются 8-разрядные регистры B-L, доступ к которым происходит через мультиплексор МПП. Регистры W и Z программно не доступны. Регистры B-L могут использоваться парами как 16-разрядные.

ПС – программный счетчик, хранящий адрес текущей выполняемой команды, а после ее выборки из памяти увеличивается в соответствии с длиной выполняемой команды в байтах.

УС – указатель стека. Хранит адрес верхушки стека, который размещается в оперативной памяти.

СП – схема приращений. Используется для изменения содержимого программного счетчика и содержимого стека.

РА – регистр адреса.

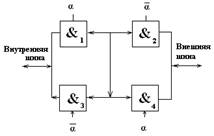

Буфер шины адреса представляет собой устройство, обеспечивающие подключение и отключение внутренней и внешней шины. Построение такого одноразрядного буфера может быть выполнено по следующей схеме:

При сигнале управления ![]() = 1 будут открыты

логические элементы 1 и 4. В результате значение с внутренней шины данных

передается на внешнюю. Если

= 1 будут открыты

логические элементы 1 и 4. В результате значение с внутренней шины данных

передается на внешнюю. Если ![]() = 0, то

значения с внешней шины данных будут поступать на внутреннюю.

= 0, то

значения с внешней шины данных будут поступать на внутреннюю.

Устройство управления и синхронизации собрано по схеме с «жесткой» логикой и формирует сигнал управления подаваемый на все элементы МП. Распределение их во времени обеспечивает сигнал синхронизации.

Помимо этого устройство

формирует сигнал ![]() при записи

информации в память или на внешнее устройство. При передачи информации в МП по

шинам данных формируется сигнал DB.

при записи

информации в память или на внешнее устройство. При передачи информации в МП по

шинам данных формируется сигнал DB.

HOLD – сигнал захвата. Формируется после окончания выполнения текущей команды до начала выполнения следующей команды.

HDLA – сигнал подтверждения сигнала захвата.

INT – запрос на прерывание. Воспринимается МП после выполнения текущей команды.

После этого, содержащаяся программа счетчика и регистра команд записывается в стек. Записанный адрес первой команды обрабатывает прерывание.

INT E – сигнал разрешения прерывания. Может быть установлен программой.

WAIT – сигнал режима ожидания МП, в котором находится МП при подготовке внешних устройств к процессу обмена информации.

READY – сигнал готовности от внешних устройств.

F1 и F2 – сигнал, поступающий от тактового генератора.

Команды МП могут быть 1-, 2-, 3-х байтными.

Для извлечения операндов (обработанных данных) используют следующие методы адресации:

1. непосредственная адресация. При этом обработка данных размещается непосредственно в теле команды во 2-м или 2-м и 3-м байтах.

2. прямая адресация. Адрес операнда размещается во 2-м и 3-м байтах. Во 2-м размещается младший байт адреса.

3. косвенная адресация. В составе 2-го или 2-го и 3-го байтах указывается регистр, содержащий адрес памяти, по которому размещаются обратные операнды.

4. регистровая. Применяется в однобайтных командах, в котором используется регистр, определяемый кодом команды.

Все команды делятся на следующие группы:

1. команды пересылки;

2. арифметические, включающие алгоритмы сложения, вычитания, инкремента, декремента. Умножение и деление выполняемой команды отрицательного числа, представляются дополнительным кодом.

3. логические: «и», «или», сдвиговые.

4. команды управления и команды ввода\вывода с внешних устройств.

5. команды перехода и вызова подпрограмм условного и безусловного перехода.

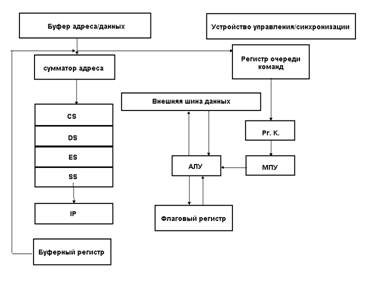

Примером 16-ти разрядного процессора является Intel-8086.

Он имеет 16-разрядную шину данных, которая мультиплексируется 16-разрядной шиной адреса. Мультиплексирование – временное разделение использования шины.

Имеется 4 старших разряда адреса, которые мультиплексируются с сигналами состояния микропроцессора. Условно микропроцессор может быть разбит на 2 части: устройство сопряжения с шиной и исполнительное устройство.

Схема микропроцессора.

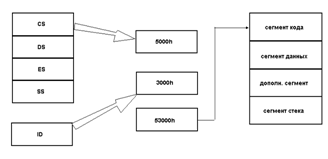

Микропроцессор содержит 16-ти разрядные сегментные регистры.

CS – для кодового сегмента

DS – регистр дополнительного сегмента

SS – сегментный регистр сегмента стека

IP – указатель на инструкцию

16-ти разрядные регистры общего назначения (AX,BX,CX,DX) , регистры указатели и индексные регистры.

SP – Stek pointer

BP – Base pointer

DI destination index

SI – source index

Флаговый регистр содержит байты, определяющие режимы работы микропроцессора и результаты работы операций. Имеется 6-ти байтная очередь команд; устройство управления и синхронизации заполняет регистры очереди командами и очереди инструкций при обработке текущей команды.

По мере освобождения очереди команд она заполняется новыми командами в соответствии с выполнением хода программы. Это дает время при выборки команд из памяти, используя команды и регистров очередных команд.

Микропроцессор имеет 20-ти разрядную шину адреса, что дает возможность адресовать 1Мб ячейке памяти.

Для доступа к этим ячейкам используется сегментация памяти с выделением сегментов по 64 Кб.(соответственно 16 разрядов. Содержимое сегмента регистра дополняется справа 16-тиричным нулем и к полученному результату добавляется 16-тиричное смещение.

Сегментные регистры

Для сегмента кода смещение хранится в регистре IP. Сумма этих значений определяет адрес байта в составе сегмента.

Регистры общего назначения могут быть разбиты на 8-ми разрядные регистры на старшую и младшую часть. AH,AL;BH,BL;CH,CL;DH,DL. – эти регистры используются в составе специальных команд.

Для доступа к сегменту стека используются специальные регистры SP и BP. Индексные регистры D1 и S1 используются при обработке операндов, занимающих последовательные байты памяти (при обработке строк символов). Значения этих регистров в определенных инструкциях добавляется к содержимому сегментного регистра и смещения.

Флаговый регистр дополнен битами по отношению к 8-миразрядной модели имеются флаги:

CF – флаг переноса из старшего разряда

OF – флаг переполнения

AF – флаг дополн. переноса (для десятичного переноса).

SF – флаг знака.

ZF – флаг нуля.

PF – флаг четности.

PF=1, если количество единиц бит четное, флаги IF,DF,TF – флаги управления.

IF – флаг разрешения прерывания (может устанавливаться программно)

DF – флаг направления при обработке строковых операндов.

TF – флаг трассировки (микропроцессор выполняет 1-у команду и останавливается).

Микропроцессор использует микропрограммное устройство управления. Тактовая частота составляет 5-8 МГц.

Intel 80286 имеет 16-разрядную шину данных, 24 – разрядную шину адреса. Содержит те же наборы регистров, 16 Мб ОЗУ. Повышена тактовая частота 12-20 MHz. Собраны модели IBM PC\AT, работающие под управлением операционной системы MSDOS, и в защищённом режиме Windows 3.11.

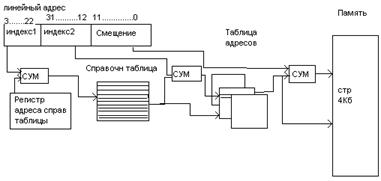

32-разрядные процессоры Intel 80386 - как и предыдущие модели, дополнялись сопроцессором для обработки чисел с плавающей точкой: Intel 80287, Intel 80387. К особенностям архитектуры надо отнести 32-разрядный адрес, обеспечивающий адресацию до 4Гб оперативной памяти, использующий следующие режимы адресации:

1. Сегментная страничная виртуальная память со стр. 4Гб, сегментами 64Тб.

2. Бесстраничная сегментная виртуальная память с сегментами по 4Гб и общим объёмом 64Тб.

3. Страничная сегментная организация памяти со страницами 4Кб и сегментами до 4Гб.

4. Бесстраничная сегментная организация памяти с сегментами до 4Гб.

Линейный адрес содержит 3 поля. Индексы по 10 бит и смещение 11 бит. 1-й индекс определяет строку в справочнике таблиц, задающую адрес таблицы адресов хранящей последнюю страницу памяти.

Элемент этой таблицы определяется 2-м индексом задаёт адрес начала страницы. Смещение определяет байт или последний байт в этой странице.

Intel 80486

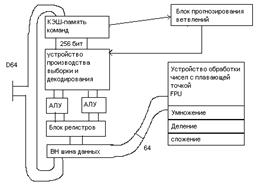

Особенность – включение сопроцессора в общую структуру.

Микроконтроллер обладает суперскалярной архитектурой, означающей то, что в каждый момент времени может выполнятся более 1-й команды за счёт наличия в составе 2-х АЛУ и устройства обработки чисел в формате с плавающей точкой (FPU), которые могут работать параллельно.

В состав входят 2 устройства внутренней кэш памяти для размещения команд и данных.

Блок прогнозирования ветвлений, позволяющий выполнить предварительную загрузку части программы, выполнение которой наиболее вероятно, что увеличивает производительность в целом на 25% .

В целочисленных АЛУ и FPU применяются конвейеры в АЛУ – 5 ступенчатые, в FPU – 8 ступенчатые, что повышает производительность, т.к. на конвейере различные компоненты выполняют свою обработку отдельных частей потоков команд.

В результате эти устройства работают параллельно, поэтому одна команда с плавающей точкой обрабатывается за 1 машинный такт, операции умножения, деления, сложения реализуются аппаратно.

Последние модели микропроцессоров отличаются введением кэш-памяти 2-го и 3-го уровня для моделей, которые размещались отдельно на микропроцессорной плате, однако, есть и другие архитектуры: AMD, которые не используют кэш-память 2,3 – уровней, но показывают хорошие результаты. Также существуют 64-разрядные процессоры.

© 2010 Интернет База Рефератов