Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Курсовая работа: Канал послідовної передачі даних

Курсовая работа: Канал послідовної передачі даних

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Національний технічний університет

“Харківський політехнічний інститут”

Кафедра обчислювальної техніки та програмування

КАНАЛ ПОСЛІДОВНОЇ ПЕРЕДАЧІ ДАНИХ

Альбом документів курсового проекту по дисципліні

“Комп’ютерна схемотехніка ”

Харків 2005

Анотація

В курсовому проект розроблено канал послідовної передачі 24-х розрядних даних із використанням мультилексорів демультиплексорів.

Розробка виконана на мікросхемах ТТЛ-логіки 155 серії. В пояснювальній записці приведені необхідн обґрунтовування, розрахунки та описи принципу дії як пристрою в цілому, так і його окремих функціональних блоків та вузлів. Виконано перевірку працездатності пристрою з використанням пакету EWB.

Альбом документів курсового проекту, крім пояснювальної записки, вміщує також структурну, принципову та функціональну схеми пристрою.

Аннотация

В курсовом проекте разработан канал последовательной передачи 24-х разрядных данных с использованием мультиплексоров и демультиплексоров.

Разработка выполнена на микросхемах ТТЛ-логики 155 серии. В пояснительной записке приведены необходимые обоснования, расчет и описание принципа действия устройства, отдельных блоков и узлов. Проведена проверка работоспособности устройства с использованием пакета EWB.

Альбом документов курсового проекта, кроме пояснительной записки, содержит также структурную, принципиальную и функциональную схемы устройства.

Annotation

There is a development of channel of sequential transfer of 24-bit data with multiplexers and demultiplexers usage in a term paper.

The development is run for microcircuits TTL – logic of 155 series. In the explanatory notes there are necessary motivations, calculations and descriptions of the principle of action of the devices as a whole and its separate functional blocks and nodes. The performance check of the device with the usage of EBM package has been carried out.

The album of the documents of the term paper contents the structure, principle and functional device schemes of the device and the explanatory notes as well.

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Національний технічний університет

“Харківський політехнічний інститут”

Кафедра обчислювальної техніки та програмування

ЗАТВЕРДЖУЮ

Завідуючий кафедрою ОТП

__________(Xxxxxxx.)

“_____”_________2005 р.

КАНАЛ ПОСЛІДОВНОЇ ПЕРЕДАЧІ ДАНИХ

Відомість проекту

Розробники

Керівник проекту

______(Xxxxxxx)

“_____”_________2005 р.

Виконавець

______(Xxxxxxx.)

“_____”_________2005 р.

Харків 2005

Формат |

Зона | Поз. | Позначення |

Найменування |

Кільк. |

Нотатки |

|

||||||||||

|

|||||||||||||||||

| Документація |

|

||||||||||||||||

| загальна |

|

||||||||||||||||

|

|||||||||||||||||

| А4 | XXXXXXX ТЗ | Технічне |

|

||||||||||||||

| завдання | 2 |

|

|||||||||||||||

| А4 | XXXXXXX ПЗ | Пояснювальна |

|

||||||||||||||

| записка | 30 |

|

|||||||||||||||

| А4 | XXXXXXX Е1 | Канал |

|

||||||||||||||

| послідовної |

|

||||||||||||||||

| передачі даних | 1 |

|

|||||||||||||||

| А3 | XXXXXXX Е2 | Канал |

|

||||||||||||||

| послідовної |

|

||||||||||||||||

| передачі даних | 1 |

|

|||||||||||||||

| А3 | XXXXXXX Е3 | Канал |

|

||||||||||||||

| послідовної |

|

||||||||||||||||

| передачі даних | 1 |

|

|||||||||||||||

| А4 | XXXXXXX ПЕ | Перелік |

|

||||||||||||||

| елементів | 1 |

|

|||||||||||||||

|

|||||||||||||||||

|

|||||||||||||||||

|

|||||||||||||||||

|

|||||||||||||||||

|

|||||||||||||||||

XXXXXXX ВП |

|||||||||||||||||

| Змін. | Літ | № докум | Підпис | Дата |

Канал послідовної передачі данихВідомість проекту |

Літ | Лист | Листів | |||||||||

| Розроб. | Xxxxxxx. | К | 2 | 2 | |||||||||||||

| Перевір. | Xxxxxxx |

НТУ "ХПІ"Кафедра ОТП |

|||||||||||||||

| Затв. | Xxxxxxx. | ||||||||||||||||

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Національний технічний університет

“Харківський політехнічний інститут”

Кафедра обчислювальної техніки та програмування

ЗАТВЕРДЖУЮ

Завідуючий кафедрою ОТП

__________(Xxxxxxx.)

“_____”_________2005 р.

КАНАЛ ПОСЛІДОВНОЇ ПЕРЕДАЧІ ДАНИХ

Технічне завдання

Розробники

Керівник проекту

______(Xxxxxxx)

“_____”_________2005 р.

Виконавець

______(Xxxxxxx.)

“_____”_________2005 р.

Харків 2005

Технічне завдання

Найменування: Канал послідовної передачі даних

Призначення: Канал послідовної передачі даних між двома зовнішніми пристроями.

Технічні характеристики:

Розрядність даних:

вхідних 24

вихідних 24

Основн елементи: MUX і DMUX

Використовувана серія мікросхем: 155

Дані для передачі і сигнал ввімкнення передачі задаються зовнішнім сигналом.

Канал послідовно передачі даних повинен бути побудован з використанням мультиплексорів і демультиплексорів, а також із додатковою індикацією передачі даних.

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

Національний технічний університет

“Харківський політехнічний інститут”

Кафедра обчислювальної техніки та програмування

ЗАТВЕРДЖУЮ

Завідуючий кафедрою ОТП

__________(Xxxxxxx.)

“_____”_________2005 р.

КАНАЛ ПОСЛІДОВНОЇ ПЕРЕДАЧІ ДАНИХ

Пояснювальна записка

Розробники

Керівник проекту

______(Xxxxxxx)

“_____”_________2005 р.

Виконавець

______(Xxxxxxx.)

“_____”_________2005 р.

Харків 2005

Реферат

Даний документ є пояснювальною запискою об'ємом 30 аркушів. В пояснювальній записці приведено 10 таблиць, 4 рисунки, використано 11 джерел літератури.

Ключові слова: КАНАЛ, МІКРОСХЕМА, ІНДИКАЦІЯ, ПОСЛІДОВНА ПЕРЕДАЧА ДАНИХ, МУЛЬТИПЛЕСКОР, ДЕМУЛЬТИПЛЕКСОР.

В курсовому проекті розроблено схему каналу послідовної передачі 24-х розрядних даних, виконану на мультиплескорах демультиплексорах.

Розробка виконана з застосуванням мікросхем ТТЛ-логіки 155 серії. В пояснювальної записці приведен обґрунтування побудови схеми, швидкодії схеми, розрахунки і опис принципу дії, як пристрою в цілому, так і його окремих функціональних блоків і вузлів. Проведено моделювання розробленого пристрою у пакеті моделювання EWB. Реалізовано індикацію передачі даних по каналу під час роботи пристрою.

Зміст

Вступ

I. Розробка структурної схеми каналу послідовної передач даних

II. Розробка функціональної схеми каналу послідовної передач даних

III. Розробка принципової схеми каналу послідовної передач даних

IV. Моделювання каналу послідовної передачі даних

V. Розрахунок основних параметрів і характеристик каналу

5.1. Розрахунок часових характеристик каналу

5.2. Розрахунок токів і потужності, що споживаються пристроєм

5.3. Розрахунок надійност пристрою

Висновки

Список використаної літератури

| Позначення |

Найменування |

Кількість |

|

||||||||||

|

|||||||||||||

| Конденсатори |

|

||||||||||||

| С1 | КМ-6-9-130 пФ +-10% ОЖО 464.023 ТУ | 1 |

|

||||||||||

| С2 | КМ-6-9-68 мкФ +-10% ОЖО 464.023 ТУ | 1 |

|

||||||||||

| С2-С39 | КМ-6-9-0,68 мкФ +-10% ОЖО 464.023 ТУ | 37 |

|

||||||||||

| Резистори |

|

||||||||||||

| R1 | МЛТ-0,125-10 кОм +- 10% | 1 |

|

||||||||||

| R2, R3 | МЛТ-0,125-100 Ом +- 10% | 2 |

|

||||||||||

| Світлодіоди |

|

||||||||||||

| VD1, VD2 | АЛ307В | 2 |

|

||||||||||

| Мікросхеми |

|

||||||||||||

| DD1-DD3, DD39-DD41 | К155ИР13 | 6 |

|

||||||||||

| DD4 | К155ЛИ1 | 1 |

|

||||||||||

| DD5 | К155АГ1 | 1 |

|

||||||||||

| DD6, DD12, DD42 | К155ТВ1 | 3 |

|

||||||||||

| DD7-DD9, DD11 | К155КП7 | 4 |

|

||||||||||

| DD10, DD23-DD26 | К155ЛН1 | 5 |

|

||||||||||

| DD13 | К155ИЕ5 | 1 |

|

||||||||||

| DD14, DD15, DD17-DD22 | К155ИД7 | 8 |

|

||||||||||

| DD16 | К155ЛА2 | 1 |

|

||||||||||

| DD27-DD38 | К155ТМ2 | 12 |

|

||||||||||

| Розняття |

|

||||||||||||

| ХР1, ХР2 | Вилка ГРП М1-61ШУ2 Кео.364.006 ДТУ | 2 |

|

||||||||||

|

|||||||||||||

|

|||||||||||||

|

|||||||||||||

XXXXXXX ПЕ |

|

||||||||||||

|

|||||||||||||

|

|||||||||||||

| Змін | Літ | № докум | Підпис | Дата |

Канал послідовної передачі данихПерелік елементів |

Літ | Лист | Листів | |||||

| Розроб. | Xxxxxxx. | К | 1 | 1 | |||||||||

| Перевірив | Xxxxxxx |

НТУ "ХПІ"Кафедра ОТП |

|

||||||||||

|

|||||||||||||

| Затв. | Xxxxxxx. |

|

|||||||||||

Технічне завдання

Найменування: Канал послідовної передачі даних

Призначення: Канал послідовної передачі даних між двома зовнішніми пристроями.

Технічні характеристики:

Розрядність даних:

вхідних 24

вихідних 24

Основн елементи: MUX і DMUX

Використовувана серія мікросхем: 155

Дані для передачі і сигнал ввімкнення передачі задаються зовнішнім сигналом.

Канал послідовно передачі даних повинен бути побудован з використанням мультиплексорів і демультиплексорів, а також із додатковою індикацією передачі даних.

Реферат

Даний документ є пояснювальною запискою об'ємом 30 аркушів. В пояснювальній записці приведено 10 таблиць, 4 рисунки, використано 11 джерел літератури.

Ключов слова: КАНАЛ, МІКРОСХЕМА, ІНДИКАЦІЯ, ПОСЛІДОВНА ПЕРЕДАЧА ДАНИХ, МУЛЬТИПЛЕСКОР, ДЕМУЛЬТИПЛЕКСОР.

В курсовому проекті розроблено схему каналу послідовної передачі 24-х розрядних даних, виконану на мультиплексорах демультиплексорах.

Розробка виконана з застосуванням мікросхем ТТЛ-логіки 155 серії. В пояснювальної записці приведен обґрунтування побудови схеми, швидкодії схеми, розрахунки і опис принципу дії, як пристрою в цілому, так і його окремих функціональних блоків і вузлів. Проведено моделювання розробленого пристрою у пакеті моделювання EWB. Реалізовано індикацію передачі даних по каналу під час роботи пристрою.

Зміст

Вступ............................................................................................................. 4

I. Розробка структурної схеми каналу послідовної передачі даних 5

II. Розробка функціонально схеми каналу послідовної передачі даних............................................................................................................ 7

III. Розробка принципової електричної схеми каналу послідовної передачі даних…………………………………………..9

IV. Моделювання каналу послідовно передачі даних... 20

V. Розрахунок основних параметрів характеристик каналу 23

5.1. Розрахунок часових характеристик каналу.......................................... 23

5.2. Розрахунок токів і потужності, що споживаються пристроєм ............ 25

5.3. Розрахунок надійност пристрою ......................................................... 26

Висновки ................................................................................................. 28

Список використаної літератури ............................................... 30

ВСТУП

Кожний складний електронний пристрій складається із окремих функціональних блоків і вузлів, що виконують окремі специфічні функції. Для об'єднання окремих блоків (наприклад в ЕОМ процесор, ОЗП, накопичувачі і ін.) у цілісну систему необхідна наявність каналів передачі даних між окремими блоками обчислювальної системи. Тобто канали передач даних дозволяють поєднати окремі вузли у цілісну систему для реалізації управління головного блоку підпорядкованими пристроями і обміну інформацією між ними під час взаємодії [1].

Важливість правильної організації і побудови каналів передачі даних полягає в тому, що часто вони є вузьким місцем в системі "пристрій – канал – пристрій", чим можуть обмежувати можливості всієї системи в цілому. Ця проблема вирішується збільшенням пропускної спроможності каналу шляхом ущільнення даних, що передаються [2], модуляцією сигналу або збільшенням кількості провідників інформаційного сигналу в самому канал передачі даних [3]. З іншого боку, при передачі даних на велику відстань поста потреба економії матеріалів і зменшення кількості жил в провіднику.

Також стоїть проблема вибору носія інформаційного сигналу: це можуть бути радіоканал різних діапазонів, провідний канал, оптичний канал і ін. Все залежить від задач, які стоять перед розробником пристрою і тих технічних рішень які він запропонує.

В даній курсовій роботі поставлено задачу розробки пристрою послідовної передачі даних по провідному каналу згідно із технічним завданням.

I Розробка структурно схеми каналу послідовної передачі даних

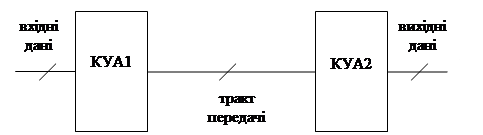

Канал передачі даних можна представити в загальному вигляд (Рис. 1.1):

КУА – канало утворююча апаратура

Рисунок 1.1 Загальна схема каналу передачі даних

Тобто, канал передачі даних представляє собою з’єднувач-провідник, визначений на схемі як тракт передачі, і каналоутворюючу апаратуру (КУА1), що готу вхідні дані до передачі, управляє процесом передачі і формує вихідні дані на іншому боці пристрою (КУА2) [4]. Саме такий принцип побудови каналу передачі даних взято нами за основу при розробці структурної схеми пристрою (XXXXXXXXXXXXX Е1).

В нашому пристрої на вході дані приймає і зберігає, протягом передачі, блок збереження вхідних даних. З його виходів послідовно, під керівництвом системи управління передачею, дані знімаються і формуються із паралельного коду у послідовний, у блоці перетворення паралельного коду у послідовний, після чого поступають в канал передачі. На іншому кінці каналу дані послідовно знімаються, знов формуються у паралельний код у блоці перетворення послідовного коду у паралельний , по завершенні передачі, записуються у блок збереження вихідних даних.

Канало-утворююча апаратура (КУА) включає світлові індикатори на вході і виході, що сигналізують про роботу пристрою. Сигналізацію виконано таким чином, що при передачі інформації маємо сигнал о зайнятості пристрою.

Процес передачі даних проходить під керівництвом блока управління передачею даних, що запускається із приходом сигналу "Start" і синхронізується блоком синхронізації передавача. Запуск передач нових даних неможливий, доки пристрій не завершить увесь цикл передачі, про що можна довідатись тільки по зміні сигналу індикатора.

ii Розробка функціональної схеми каналу послідовної передачі даних

Згідно із структурою схемою, розглянутою в попередньо главі, проаналізуємо, які мікросхеми потрібні для реалізації технічного завдання и розробимо функціональну схему пристрою (XXXXXXXXXXXXX Е2).

Блок збереження вхідних даних можна реалізувати на баз регістрів на 24 входи (DD1), загрузка даних в ці регістри відбувається із приходом логічної одиниці сигналу "start".

24-розрядні дані із виходів регістрів поступають на входи селектора–мультиплексора (24→1) (DD6), що, згідно із керуючими сигналами блока управління передачею даних, формує із паралельного коду послідовний.

Послідовні дані побітно поступають на вхід демультиплексора (1→24) (DD7), який, згідно із управляючими сигналами, що поступають із блока управління (DD2-DD5, DD7), формує на виході паралельний код, в якому і-й розряд відповідає біту, що прийшов на вхід, інші розряди заповнені "1". Тобто інформаційним є лише і-й біт, заданий кодом на входах А1-А5 демультиплексора.

Паралельно із демультиплексором ми використали дешифратор на 24 входи (DD8), що згідно з управляючими сигналами А1-А5, формує на відповідному виході управляючий сигнал "1", інші виходи – "0".

Дані з виходів демультиплексора поступають на інформаційн входи групи D-тригерів (24 шт.) (DD9), а управляючі сигнали із виходів дешифратора (DD8) – на управляюч входи цієї групи D-тригерів. Завдяки цьому послідовний код із тракту передачі послідовно записується у вигляді паралельного в D-тригери так, що на виходах групи D-тригерів, по завершенні передачі останнього біта, сформовано 24-розрядний паралельний код, який відповідає даним, що прийшли на вхід нашого пристрою.

Паралельні дані із виходів групи D-тригерів поступають в блок збереження вихідних даних (DD10), що реалізовано на групі регістрів, які завантажують результуючі дан по управляючому сигналу на 24-му виході дешифратора, що означає завершення передачі.

Увесь процес передачі проходить під керівництвом блока управління передачею даних, який із приходом сигналу "Start" завантажує вхідні дані у вхідні регістри і потім формує сигнали А1-А5, що задають числа від 0 до 23, які відповідають за передачу відповідного біту даних. Блок управління передачею даних можна поділити на дві частини: лічильник від 0 до 23 (DD7) і тригер, що запирає. Тригер представляє собою RS-тригер (DD4), пов'язаний з своїм входом S зворотним зв’язком через елемент "2 ТАК" (DD2). Коли пристрій не працює на виход Q' тригеру встановлений сигнал "1". Коли приходить сигнал "Start", елемент "2 ТАК" пропускає імпульс, по якому завантажуються вхідні регістри (DD1), і тригер встановлюється в "1", після чого на виході Q' встановлюється "0", який запирає сигнал " Start " через схему "2 ТАК". В цей час на виході тригера Q встановлюється "1", що через інший елемент "2 ТАК" (DD5) відкрива шлях синхроімпульсам із блоку синхронізації передачі даних (DD3) на вхід лічильника із модулем рахунку 24. На виході лічильника (DD7) під дією синхроімпульсів формується керуючий код А1-А5. Коли лічильник дорахує до 23, він встановлюється в "0" і поступає сигнал "1" на вхід R тригера і тригер встановлюється в "0", в результаті чого відкривається шлях для нового сигналу "Start" і закривається шлях для синхроімпульсів. Таким чином схема блока управління передачею даних запускається із приходом "1" на вхід "Start", після чого запирається і не реагує на нього доки не виконає рахунок від 0 до 23, тобто повний цикл передачі. Після цього вона знов відкривається і чека наступного сигналу "Start" щоб почати передачу.

Блок управління передачею даних синхронізується блоком синхронізації (DD3), який реалізований на одновібраторі, що вмикається сигналом "1" на вході "Start".

III Розробка принципово електричної схеми каналу послідовної передачі даних

Згідно із розробленою функціональною схемою для побудови принципової електричної схеми каналу послідовної передачі даних (XXXXXXXXXXXXX Е3) вибираємо реальні мікросхеми і обґрунтовуємо схемотехнічні рішення, прийняті при використанн кожної з них.

Під час розробки принципової електричної схеми були використан регістри, мультиплексори, демультиплексори, тригери, логічні елементи і одновібратор, що були надані 155-ою серією мікросхем.

Регістри

В якості регістрів використаємо мікросхеми К155ИР13 (DD1-DD2, DD40-DD41). Мікросхема представляє собою універсальний зсувний регістр, його таблиця стинності і функціонування має наступний вигляд (Табл. 3.1) [5, 6]:

Таблиця 3.1 Таблиця істинності і функціонування К155ИР13

| MODE | SERIAL | PARALLEL | OUTPUTS | ||||||||

| R' | S1 | S0 | C | LEFT | RIGHT | D1 ... D8 | Q1 | Q2 | ... | Q7 | Q8 |

| 0 | x | x | x | x | x | x | 0 | 0 | 0 | 0 | |

| 1 | x | x | 0 | x | x | x | Q10 | Q20 | Q70 | Q80 | |

| 1 | 1 | 1 | POS | x | x | d1...d8 | d1 | d2 | d7 | d8 | |

| 1 | 0 | 1 | POS | x | 1 | x | 1 | Q2n | Q7n | Q8n | |

| 1 | 0 | 1 | POS | x | 0 | x | 0 | Q2n | Q7n | Q8n | |

| 1 | 1 | 0 | POS | 1 | x | x | Q1n | Q2n | Q7n | 1 | |

| 1 | 1 | 0 | POS | 0 | x | x | Q1n | Q2n | Q7n | 0 | |

| 1 | 0 | 0 | x | x | x | x | Q10 | Q20 | Q70 | Q80 | |

Ми використовуємо регістри лише як буферні елементи, тому сигнал "Load" (завантажити) одночасно подається на входи C, S0, S1, по передньому фронту якого дані на входах D1-D8 поміщуються в регістр, в нших випадках регістр зберігає дані. Входи Left і Right не використані, а на вході збросу R завжди "1".

Мультиплексори

В якост блока перетворення паралельних даних в послідовні використано мультиплексори К155КП7 (DD7-DD9, DD11). Таблиця х істинності і функціонування приведена нижче и має наступний вигляд (Табл. 3.2) [5, 6]:

Таблиця 3.2 Таблиця істинності і функціонування К155КП7

| Select | Strobe | Outputs | |||

| A3 | A2 | A1 | G' | Q | Q' |

| x | x | x | 1 | 0 | 1 |

| 0 | 0 | 0 | 0 | D1 | D1 |

| 0 | 0 | 1 | 0 | D2 | D2 |

| 0 | 1 | 0 | 0 | D3 | D3 |

| 0 | 1 | 1 | 0 | D4 | D4 |

| 1 | 0 | 0 | 0 | D5 | D5 |

| 1 | 0 | 1 | 0 | D6 | D6 |

| 1 | 1 | 0 | 0 | D7 | D7 |

| 1 | 1 | 1 | 0 | D8 | D8 |

На входи A1-A3 подаються селекторні управляючі сигнали, що задають котрий з восьми входів D1-D8 буде скомутований на виходи Q і його інверсний аналог Q'.

Логічну функцію мультиплексора К155КП7 можна представити в наступному вигляді [5]:

Q = D1A1'A2'A3' + D2A1A2'A3' + D3A1'A2A3' + D4A1A2A3' +

+ D5A1'A2'A3 + D6A1A2'A3 + D7A1'A2A3 + D8A1A2A3.

На стробуючому вході завжди "0".

В серії К155 нема мультиплесора на 24 входи, тому необхідний мультиплексом, зібраний на мультиплексорах К155КП7, має пірамідальну структуру [4]. На першій сходинці сигнали селектуються по сигналам А1-А3, на другій – по сигналам А4-А5, при цьому з останньої сходинки сформований послідовний код знімається з інверсного виходу.

Така побудова мультиплексорів забезпечує селекцію 24-х нформаційних сигналів зі входів на один вихід під керівництвом адресних сигналів А1-А5.

Демультиплексори, дешифратори

Перетворення послідовних даних в паралельний код і дешифрація управляючих сигналів А1-А5 реалізована на мікросхемі К155ИД7 – дешифратор-демультиплексор (DD14-DD15, DD17-DD22). Таблиця стинності і функціонування має наступний вигляд (Табл. 3.3) [5, 6]:

Таблиця 3.3 Таблиця істинності і функціонування К155ИД7

| Select | |||||||||||||

| C2' | C1 | C3' | A3 | A2 | A1 | Q1 | Q2 | Q3 | Q4 | Q5 | Q6 | Q7 | Q8 |

| x | x | 1 | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| x | 0 | x | x | x | x | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 0 | x | x | x |

Output corresponding to stored address 0; all others 1 |

|||||||

Технічне завдання вимагає реалізувати передачу 24-розрядних даних, тому існує потреба у 5→24 дешифраторі і демультиплексорі. Серія К155 не містить таких мікросхем, тому необхідн елементи побудовані на мікросхемах меншої розрядності К155ИД7 (3→8). Мультиплексор має пірамідальну структуру [4]. Його перша сходинка (DD15), згідно з управляючими сигналами А4-А5, розподіляє інформаційний сигнал на три виходи, які потім демультиплексуються на другій сходинці (DD17-DD19) згідно з управляючими сигналами А1-А3 на 24 виходи. Інформаційний вхід – С1, на входи С2' і С3' подано "0".

Особливістю мікросхеми К155ИД7 є те, що на виході формується інверсний інформаційний сигнал. Тому на вхід першої сходинки демультиплесора поступає інвертований інформаційний сигнал (він формується на інверсному виході другої сходинки мультиплексора). Інверсний нформаційний сигнал перетворюється на першій сходинці у прямий, а потім знов інвертується на другій сходинці демультиплексора [2].

Дешифратор сигналу А1-А5 на 24 виходи має структуру, подібну структурі демультиплексора [4]. На першу сходинку дешифратора (DD14) поступають управляючі сигнали А4-А5, що формують "0" на одному із виходів Q1-Q3. Інформація на виходах дешифратора першої сходинки інвертується (DD10.3-DD10.5) і сигнал "1" (інверсний "0") управляє одним із трьох дешифраторів друго сходинки (DD20-DD22) згідно з управляючими сигналами А1-А3. На виходах дешифраторів розміщені інвертори (DD23-DD26), що інвертують сформований код. На інформаційний вхід (С1) дешифратора першої сходинки поступа "1", на інформаційні входи (С1) дешифраторів другої сходинки поступають двічі проінвертовані сигнали з виходів Q1-Q3 дешифратору першої сходинки. На входи С2' і C3' подано "0".

D-тригери

Проміжне збереження результатів передачі реалізовано на здвоєних D-тригерах (DD27-DD38). Використан мікросхеми типу К155ТМ2. Таблиця істинності і функціонування одного D-тригера зображена нижче (Табл. 3.4) [5, 6].

Таблиця 3.4 Таблиця істинності і функціонування К155ТМ2

| PRE | CLR | C | D | Q | Q' |

| 0 | 1 | x | x | 1 | 0 |

| 1 | 0 | x | x | 0 | 1 |

| 0 | 0 | x | x | 1 | 1 |

| 1 | 1 | POS | 1 | 1 | 0 |

| 1 | 1 | POS | 0 | 0 | 1 |

| 1 | 1 | 0 | x | Hold | |

12 корпусів К155ТМ2 забезпечують 24 окремих D-тригери. На них почергово з відповідних виходів демультиплексора записуються дані під керівництвом дешифратора.

Тобто на нформаційні D-входи D-тригерів подається паралельний код з виходів демультиплексора, а на управляючі C-входи D-тригерів подається код, сформований дешифратором. Таким чином, при передачі n-го біту на n-му виход дешифратора формується "1", що змушує n-й D-тригер завантажити біт, сформований на n-му виході демультиплексора. Тобто на D-тригерах послідовно побітно збирається 24-розрядне слово, що передається каналом передачі. Слід зазначити, що дані знімаються з інверсних виходів, тому на D-тригерах формуються проінвертовані дані, це означає, що дані для завантаження в вихідні регістри (DDM39-DD41) слід знімати з інверсних виходів.

Одновібратор

Одновібратор задає синхросигнали, він реалізований на мікросхемі К155АГ1, таблиця істинност функціонування якої приведена нижче (Табл. 3.5) [5, 6].

Таблиця 3.5 Таблиця істинності і функціонування К155АГ1

| Входи | Вихід | ||

| A1' | A2' | B | Q |

| L | x | H | L |

| x | L | H | L |

| x | x | L | L |

| H | H | ↓ | L |

| H | ↓ | H | 1 |

| ↓ | H | H | 1 |

| ↓ | ↓ | H | 1 |

| L | x | ↑ | 1 |

| x | L | ↑ | 1 |

На входи A1' A2' подано "0", що відповідає сигналу "L". Одновібратор запускається із приходом "1" ("H") на вхід B і не ма можливості перезапуску (не реагує на вхідні сигнали доки не завершиться цикл роботи).

На виход Q мікросхеми формуються синхроімпульси, які задаються елементами C1 і R1.

Частота вибирається згідно із загальною затримкою на мікросхемах каналу передачі і пошук буде розглянуто в пункті 5.1 ("Розрахунок часових характеристик каналу"). Відповідно до частоти вибираються і C1, R1.

Лічильник

Технічне завдання вимагає реалізувати передачу 24-розрядних даних, тому з'являється необхідність формувати управляючі сигнали номіналом від 0 до 23 (А1-А5), які будуть керувати послідовністю побітной передачі даних по каналу. По завершенні циклу рахунку процес передачі має завершитись.

Дані задач реалізує лічильник із модулем рахунку 24. Серія К155 нада лічильник К155ИЕ5, що має модуль рахунку 16 (DD13). Його таблиця істинності і функціонування приведена нижче (Табл. 3.6) [5, 6].

Таблиця 3.6 Таблиця істинності і функціонування К155ИЕ5

| Reset in | Output | ||||

| R01 | R02 | Q1 | Q2 | Q3 | Q4 |

| 1 | 1 | 0 | 0 | 0 | 0 |

| 0 | x | Count | |||

| x | 0 | Count | |||

Вхід С1 нформаційним, а на С2 заведений сигнал з Q1. При подач на R01 і R02 "1" лічильник обнулюється.

Для того, щоб розширити лічильник до модуля рахунку 24 використано додатково Т-тригер (DD12), який, з'єднаний послідовно із лічильником (DD13), утворює лічильник з модулем рахунку 32 (вихід Q тригера подається на вхід С1 лічильника) [4].

Т-тригер побудовано на основі мікросхеми К155ТВ1 – JК-тригера з логікою "3 ТАК" на вході. Таблиця істинності і функціонування цього тригеру приведена нижче (Табл. 3.7) [5, 6].

Таблиця 3.7 Таблиця істинності і функціонування К155TB1

| P' | S' | C | J | K | Q | Q' |

| 0 | 1 | x | x | x | 1 | 0 |

| 1 | 0 | x | x | x | 0 | 1 |

| 0 | 0 | x | x | x | UNSTABLE | |

| 1 | 1 | 1 | 0 | 0 | Q0 | 'Q0 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | Toggle | |

Входи J1-J3, K1-K3, S' об’єднан на них подано "1". В такій побудові тригер працює як Т-тригер, вхід С є інформаційним і на нього подаються синхросигнали, вхід R' встановлю тригер в "0" [4]. Обмеження модуля рахунку до 24 реалізовано завдяки елементу "8 ТАК – НІ" (DD16) (мікросхема К155ЛА2) [5, 6]. Якщо на всі входи мікросхеми прийшли "1", то на виході схеми буде "0", в інших випадках – буде "1". 23 в двійковому представленні виглядає так: 10111. Тому сигнали А5, А3-А1 з виходів зібраного лічильника подається на входи елемента "8 ТАК НІ" напряму, а сигнал А4 інвертується (DD10.2). На нші вільні входи елемента завжди подається "1". Цим досягається те, що коли лічильник сформує код 23 (10111), то на всіх входах елемента "ТАК – НІ" будуть всі "1" і мікросхема видасть сигнал "0". Цей сигнал поступить напряму на вхід R' Т-тригера (DD12) і проінвертований нвертором (DD10.1) подається на входи R01 і R02 лічильника (DD13), що означа встановлення повного лічильника в "0" – завершення циклу рахунку [4].

Тригери

Окрім тригера DD12, використаного як Т-тригер для розширення лічильника, схема містить ще два тригери, які працюють як RS-тригери: управляючий тригер (DD6) і тригер індикації (DD42) приймача. Входи J1-J3, K1-K3 об'єднан на них подано "0", а на вхід С – "1". Згідно із таблицею істинност функціонування (Табл. 3.7), з приходом "1" на вхід R' і "0" на вхід S' тригер встановлюється в "1", інакше – в "0".

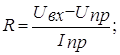

Індикатори

Згідно із технічним завданням передача даних по каналу має супроводжуватись індикацією процесу передачі даних. Ми використали світлодіоди з обох боків каналу передачі даних, що випромінюють світло доки відбувається передача, а коли пристрій в режимі чекання вхідних даних – індикатори неактивні. Це реалізовано підключенням входу світлодіода VD1 послідовно з резистором R2 до виходу Q управляючого тригера DD6 в передатчику, підключенням світлодіода VD2, послідовно з резистором R3, до тригеру ндикації DD42 (він встановлюється в "1" із передачею 0-го біту, і встановлюється в "0" із передачею 23-го біту). Використано світлодіоди АЛ307В, що випромінюють зелене світло [7]. Оскільки пристрій побудовано на ТТЛ-мікросхемах, то на вході світлодіода встановлена напруга 4,5 В.

Технічн характеристики АЛ307В: Uпр (постійна пряма напруга) не більше 2,8 В, Iпр (прямий струм) – 20 мА (Iпрmax = 22 мА) [7]. Згідно з технічними характеристиками діодів вибрано резистори R2 і R3 [8]:

![]() [Ом].

[Ом].

Таким чином, вибираються резистори R2 і R3 типу МЛТ – 0,125–100 Ом +-10% (округлення виконуються в сторону збільшення для отримання запасу надійності).

Логічні елементи

В схемі використано елементи "2 ТАК" (DD4.1, DD4.2) разом з тригером, що запирає. Вони входять у мікросхему К155ЛИ1, що містить чотири окремих елементів "2 ТАК" [5, 6].

Елементи "НІ", використані в схемі встановлення в "0" лічильника (DD10.1, DD10.2) і в дешифраторі (DD10.3-DD10.5, DD23-DD26), були взяті з мікросхем К155ЛИ1, як містять по шість елементів "НІ".

Живлення схеми

На вхід 63 розняття ХР1 подається живлення +5 В, що необхідне для мікросхем ТТЛ, на 64-му вході розняття ХР1 – GND. Між лінією +5 В і GND паралельно включені конденсатори. Конденсатор С2 вибрано типу КМ-6-9-68мкФ+-10% ОЖО 464.023ТУ. Кількість інших конденсаторів визначається кількістю і типом мікросхем, що складають схему. Загальна кількість мікросхем 42, серед них 7 мікросхем, що реалізують логічні елементи. Таким чином маємо 36 конденсаторів (С3-С39) типу КТ-6-9-0,068мкФ+-10% ОЖО 464.023ТУ (по одному конденсатору на 10 мікросхем-логічних елементів і на кожну іншу мікросхему – по одному конденсатору).

Послідовність функціонування каналу передачі даних

Узагальнюючи все сказане в даній главі пояснимо послідовність функціонування розробленого пристрою і принципи, на яких ґрунтується його робота.

Канал послідовно передачі даних має розняття (ХР1) для шини вхідних даних, на входи якого (2-25) поступають вхідні дані для передачі, а сигнал управління "Start" поступає на вхід 1.

В режимі чекання тригер, що запирає (DD6), встановлений в "0" запирає, через елемент "2 ТАК" (DD4.2), шлях для синхроімпульсів. На вход VD1 нульова напруга і світлодіод не випромінює. Тригер (DD42) теж встановлений в "0" і відповідний світлодіод VD2 теж не випромінює.

Із приходом сигналу початку передачі "Start" на вхід 1 (сигнал "1") одновібратор (DD5) запускається і починає формувати синхроімпульси. В цей же час сигнал "Start", через відкритий елемент "2 ТАК" (DD4.1), поступає на входи C, S0 і S1 регістрів (DD1-DD3) і завантажуються дані для передач з входів 2-25 розняття ХР1. Тригер, що запирає (DD6), встановлюється в 1, на виході Q' встановлюється "0" і він через елемент "2 ТАК" (DD4.1) запирає вхід схеми для управляючих сигналів (на час передачі завантажених даних). На виході Q тригера DD6 встановлюється "1", що вмика світлодіод VD1 і через елемент "2 ТАК" (DD4.2) відкриває шлях для синхроімпульсів на вхід лічильника (DD12, DD13).

Лічильник під керівництвом синхроімпульсів формує п’яти-розрядні управляючі сигнали А1-А5 (DD7-DD9, DD11), які поступають на мультиплексор змушують його вибрати один біт із виходів регістрів і передати в канал послідовно передачі даних.

Управляючі сигнали А1-А5 поступають на приймач і змушують демультиплексор взяти інформаційний біт з каналу передачі і скомутувати на один із виходів. Одночасно із цим на виходах дешифратора (DD14, DD20-DD22, DD10.3DD10.5, DD23-DD26) на відповідному місці, номер якого задається сигналами А1-А5, формується управляючий сигнал, що змушує відповідний тригер (DD27-DD38) зберегти потрібний інформаційний сигнал з виходу демультиплексора. Якщо передається тільки перший біт, тригер індикац (DD42) також встановлюється в "1", в результаті чого засвітлюється світлодіод VD2. Процес послідовного зняття даних мультиплексором потім побітного їх передавання по каналу, із записом у відповідні тригери, виконується 24 рази.

Коли на виході лічильника сформується число 23, на елементі контролю модулю рахунку (DD16) сформується управляючий сигнал "1", що обнуляє лічильник (DD12, DD13) і тригер DD6.

На виході Q тригеру, що запирає (DD6), сформується сигнал "0", що, через елемент "2 ТАК" (DD4.2), закриє шлях для синхроімпульсів на вхід лічильника і світлодіод передавача VD1 припинить випромінювати світло. "1" на виході Q' тригера відкриє шлях, через елемент "2 ТАК" (DD4.1), для сигналу "Start" і схема переведеться в режим чекання. В цей час по каналу відбувається передача останнього 24-го біта даних і он запишеться у відповідний D-тригер. На 24-му виході дешифратора сформується управляючий сигнал (по ньому відбувається завантаження 24-го біта у D-тригер), який обнуляє регістр DD42, після чого індикатор VD2 припиняє випромінювати, по управляючому сигналу також відбувається завантаження із D-тригерів (DD27-DD38) паралельного коду у вихідні регістри (DD38-DD41). Вихідні дані будуть зберігатися в регістрах, доки не завантажаться нові дані. Утримувач може зняти результуючі передан дані із виходів 26-49 розняття ХР2.

IV Моделювання каналу послідовної передачі даних

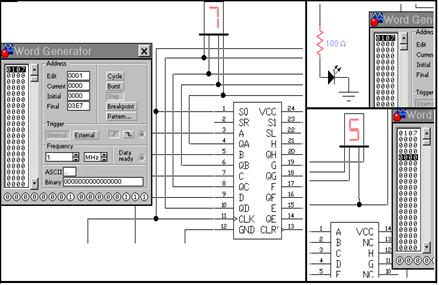

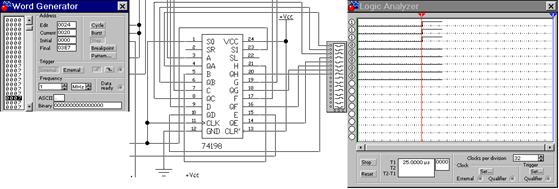

Для перевірки роботоспроможност спроектованого пристрою і розкриття його особливостей було виконано моделювання каналу передачі даних за допомогою пакета програм "Electronics Workbench" 5.12 (EWB 5.12).

В EWB було зібрано спрощену схему каналу передач (Рис. 4.1): можливість передати лише 8-бітний код; деякі логічні елементи замінен стандартними аналогами EWB; за відсутності в EWB мікросхеми одновібратора К155АГ1 використані синхроімпульси вбудованого в EWB генератора; замість мікросхем серії К155 використані їх аналоги із 741-ї серії. Отримані слайди демонструють правильність роботи моделі.

Аналіз роботи пристрою проводився в покроковому режимі. На першому кроці на інформаційні входи пристрою було подано код "7", а на вхід Start код запуску "1". В результат ми спостерігали встановлення кодової комбінації 7 в регістрі збереження вхідних даних і запуск роботи пристрою, що було індуковано загоранням світлодіоду (Рис. 4.2).

Після цього було покрокове виконання роботи схеми, під час чого ми могли спостерігати як лічильник послідовно видає управляючі сигнали, за якими спрацьовують інші елементи схеми і збирають на D-тригерах готовий код. Так, на п’ятій ітерації на виходах лічильника встановився код "5" (Рис. 4.2), що означає передачу п’ятого біту.

Процес передачі виконується за 24 ітерації, після чого в вихідний регістр записуються готові дані. Це ми могли спостерігати за допомогою підключення цифрового аналізатору до виходів регістру, в якому зберігається результат передачі (Рис. 4.3).

Слід також відмітити, що на виході пристрою результати попередньої передачі будуть зберігатися увесь час доки не завантажаться дані наступної передачі.

Рисунок 4.2 Моделювання передачі даних

Рисунок 4.3 Отримання результатів передачі

Таким чином, проведене моделювання показало роботоспроможність розробленого пристрою і підкреслило правильність прийнятих схемотехнічних рішень.

V Розрахунок основних параметрів і характеристик пристрою

5.1 Розрахунок часових характеристик

Для розрахунку часових характеристик розробленого пристрою і генератору синхроімпульсів (частоту), тобто швидкодії каналу передачі, необхідно знати часову затримку на елементах мікросхеми. Знайдемо середні значення цієї затримки і складемо таблицю (Табл. 5.1) [5, 6].

Таблиця 5.1 Затримки на мікросхемах

| Тип мікросхеми |

01 tзат, нс |

10 tзат, нс |

Середня tзат, нс |

| К155АГ1 | 80 | 70 | 75 |

| К155ИД7 | 32 | 32 | 32 |

| К155ИЕ5 | 36 | 34 | 35 |

| К155ИР13 | 40 | 38 | 39 |

| К155КП7 | 32 | 34 | 33 |

| К155ЛА2 | 15 | 22 | 18,5 |

| К155ЛИ1 | 19 | 27 | 23 |

| К155ЛН1 | 15 | 22 | 18,5 |

| К155ТВ1 | 40 | 25 | 32,5 |

| К155ТМ2 | 40 | 25 | 32,5 |

Розрахуємо частоту, яку необхідно задати на генераторі імпульсів (DD5). Для цього знайдемо затримку на елементах схеми [4, 8], що керовані генератором імпульсів, яка дорівнює τген – довжині імпульсу генератора:

τген = tзат.ли1 + tзат.тв1 + tзат.ие5 + max(tзат.лн1 + tзат.ла2 + tзат.лн1 + tзат.тв1; tзат.кп7 +

+ tзат.кп7 + max(tзат.ид7 + tзат.ид7; tзат.ид7 + tзат.лн1 + tзат.ид7 + tзат.лн1) +

+ max(tзат.тм2 + tзат.тв1));

τген = 23 + 32,5 + 35 + max(18,5*2 + 18,5 + 32,5; 33*2+ max(32*2; 32*2 +

+ 18,5*2) + max(32,5 + 32,5)) = 23 + 32,5*2 + 35 + 33*4 + 18,5*2 =

= 292[нс].

Скважність (Ө) імпульсів візьмемо рівною 2. Звідси знайдемо період імпульсів (Тген) [8]:

Тген = Ө τген;

Тген =2*292 = 584[нс].

Однак період слідування мпульсів пов’язаний із R1 і C1 наступною формулою [8]:

Тген = 0,45*R*C1.

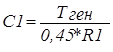

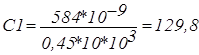

Задамо номінал R1 – 10 кОм (регістр R1 виберемо таким: МЛТ-0,125-10 кОм +- 10%). Тод знайдемо ємність конденсатору С1:

;

;

[пФ].

[пФ].

Виберемо С1 – КМ-6-9-130 пФ+-10%ОЖО 464.023ТУ.

Згідно із вибраними номіналами R1 і С1 знайдемо період імпульсів, які буде створювати генератор:

Тген = 0,45*10*103*130*10-12 = 585 [нс].

Щоб знайти швидкодію всього пристрою знайдемо затримку на елементах при завантаженні даних у вхідн вихідні регістри, та час на 24 цикли передачі кожного біту. Це буде максимальний період слідування сигналів Start.

Тсх. = tзат.ир13 + Тген + tзат.ир13;

Тсх. = 2*39 + 24*585 = 14118 [нс].

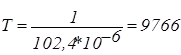

Максимально доступну частоту передачі даних схемою можна визначити за формулою [8]:

![]() ;

;

[кГц].

[кГц].

Тобто із такою максимальною частотою можна зовнішньому пристрою подавати дані на входи нашого пристрою. (Схема не буде реагувати на вхідні дані доки не завершить передачу даних, що поступили до цього.)

5.2 Розрахунок струмів і потужності, що споживаються пристроєм

Струми, що споживаються кожною мікросхемою визначимо використовуючи паспортні дані на ці мікросхеми (Табл. 5.2) [5, 6].

Таблиця 5.2 Струми, споживані мікросхемами

| Тип мікросхеми |

Іспож, мА |

| К155АГ1 | 25 |

| К155ИД7 | 55 |

| К155ИЕ5 | 53 |

| К155ИР13 | 116 |

| К155КП7 | 48 |

| К155ЛА2 | 6 |

| К155ЛИ1 | 33 |

| К155ЛН1 | 33 |

| К155ТВ1 | 20 |

| К155ТМ2 | 20 |

| АЛ102В | 20 |

Струм, що споживається схемою (Ік) визначається як сума всіх струмів, спожитих окремими мікросхемами [4, 8]:

Ік = Іаг1 + Іил7*8 + Іие5 + Іир13*6 + Ікп7*4 + Іла2 + Іли1 + Ілн1*4 + Ітв1*3+

+ Ітм2*12 + Іал*2;

Ік = 25 + 55*8 + 53 + 116*6 + 48*4 + 6 + 33 + 33*4 + 20*3 + 20*12 =

= 1917[mA].

Потужність, що споживається каналом визначається за наступною формулою [4, 8]:

P = U*Iк.

Напруга живлення 5 В+-10%. Виходячи з цього визначимо потужність схеми (беремо максимально можливу напругу 5,5 В):

P = 5,5*1917*10-3 = 10,5435[Вт]

Тобто, споживана потужність не перевищує 10,6 Вт. Таким чином для функціонування пристрою необхідно джерело енергії 5 В потужністю 10,6 Вт.

5.3 Розрахунок надійності пристрою

Надійність пристрою визначається інтенсивністю відмов, кількістю пристроїв, що відмовили за одиницю часу, поділеною на загальну кількість пристроїв.

Ми вважаємо, що вірогідність відмови кожної мікросхеми взаємонезалежна від інших мікросхем і відмова однієї мікросхеми причиною відмови усього пристрою в цілому. Виходячи із цього, маємо формулу підрахунку нтенсивності відмов для всього пристрою в цілому, що знаходиться як сума добутку нтенсивностей відмов кожного типу мікросхем на кількість таких мікросхем:

;

;

![]() – інтенсивність відмов елементів і-го типу,

– інтенсивність відмов елементів і-го типу,

![]() – кількість елементів і-го типу.

– кількість елементів і-го типу.

Напрацювання на відмову (характеризує час, протягом якого пристрій має працювати безвідмовно) визначається як обернена величина до інтенсивності відмов:

![]() .

.

Інтенсивність відмов елементів пристрою візьмемо із таблиці 5.3.

Таблиця 5.3 Таблиця відмов різних типів елементів

| Тип елемента | Інтенсивність відмов, 1/год |

| Мікросхеми |

0,85*10-6 |

| Резистори |

0,9*10-6 |

| Конденсатори |

1,6*10-6 |

| Світло-діоди |

0,8*10-6 |

В схемі пристрою використано 42 мікросхеми, 3 резистори, 39 конденсаторів, 2 світлодіода. Знайдемо інтенсивність відмов і напрацювання на відмову каналу послідовної передачі даних:

λ = (42*0,85 + 3*0,9 + 39*1,6 + 2*0,8)*10-6 = 102,4*10-6 [1/год];

[год].

[год].

![]() Оскільки нами були не враховані деякі елементи

схеми і інші ризики, будемо вважати, що загальне напрацювання на відмову склада

4500 годин.

Оскільки нами були не враховані деякі елементи

схеми і інші ризики, будемо вважати, що загальне напрацювання на відмову склада

4500 годин.

Висновки

В даному курсовому проекті розроблено пристрій "Канал послідовної передачі даних". Він реалізу послідовну передачу 24-розрядних даних за допомогою використання мультиплексорів демультиплексорів. Додатково реалізовано індикацію процесу передачі даних на світло-діодах. При побудові використано мікросхеми ТТЛ-логіки 155 серії.

Розроблено структурну, функціональну і принципову електричну схеми пристрою, проведено моделювання пристрою в пакеті моделювання "Electronics Workbench" 5.12, отримані часові діаграми і показання допоміжних числових індикаторів пояснюють роботу пристрою і демонструють правильність прийнятих технічних рішень.

Розроблений пристрій складається із 42 мікросхем, 39 конденсаторів, 3 резисторів і 2 світлодіодів.

Потужність, що споживається від джерела напруги 5 В складає 10,6 Вт.

Напрацювання на відмову не менше 4500 годин.

Виконано розробку конструкторської документації – креслення структурної, функціональної та принципово електричної схем пристрою.

Розроблена схема характеризується достатньою надійністю і прийнятним енергоспоживанням, а також має значні переваги, серед яких:

1) Вхідні дан один раз записуються в регістри і не зсуваються, що гарантує їх правильність і виключа ситуацію збою при зсуві;

2) Передані результуюч дані зберігаються в вихідному регістрі протягом всього циклу послідовної передач наступного блоку даних, що надає деяку свободу дії приймача;

3) На період передачі пристрій блокується від вхідних управляючих сигналів, що гарантує прихід наступних даних лише тоді, коли повністю завершиться передача попередніх даних, що гарантує стійкість даних;

4) Індикація передачі дає можливість користувачу візуально відслідковувати процес передач готовність пристрою прийняти новий блок інформації.

Даний пристрій може бути використано як функціональний блок EBM для передачі сигналів управління між пристроями, або як канал односторонньої передачі даних на відстані.

СПИСОК ВИКОРИСТАНОЇ ЛІТЕРАТУРИ

1. Калабеков Б.А. Цифровые устройства и микропроцессорные системы: Учебник для техникумов связи. – 2-е – изд. – М.: Радио и связь, 1997. – 338с.

2. Ямпольский В.С. Основы автоматики и электронно-вычислительной техники. – М.: Просвещение, 1991. 223с.

3. Аналоговые и цифровые интегральные микросхемы: Справочное пособие / Под ред. М.Р. Якубовского. – М.: Радио и связь, 1990. – 312с.

4. Опадчий Ю.Ф. Аналоговая и цифровая электроника. - М.: Радио и связь, 1996. – 768 с.

5. Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1988. – 220с

6. Справочник по интегральным мікросхемам / Б.В. Тарабрин, С.В. Якубовский, Н.А. Барканов и др.; Под ред. Б.В. Тарабрина. 2-е изд., перераб. и доп. – М.: Энергия, 1981. – 816с.

7. Справочник по полупроводниковым диодам, транзисторам и интегральным схемам. / Под общ. Ред. Н.Н. Горюнова. Изд. 4-е, перераб. и доп. – М.: Энергия, 1976. – 744с.

8. Токхейм Я. Основы цифровой электроники. – М.: Мир, 1988. – 420с.

9. ГОСТ 2.102-68. Виды и комплектность конструкторской документации. – М., 1988.

10. ГОСТ 2.105-79. Общие требования к текстовым документам. – М., 1988.

11. ГОСТ 2.708-81. Правила выполнения электрических схем цифровой вычислительной техники. – М., 1988.

© 2010 Интернет База Рефератов