Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Курсовая работа: Вычислительная система обработки данных в реальном времени

Курсовая работа: Вычислительная система обработки данных в реальном времени

ВведениеКурсовой проект выполняется с целью закрепления знаний по курсу «Организация ЭВМ, комплексов и систем» и развития навыков самостоятельного проектирования вычислительных систем.

В курсовом проекте разрабатывается вычислительная система (ВС) обработки данных в реальном времени, состоящая из устройства ввода (УВ) и ПЭВМ. Входным сигналом является аналоговое напряжение. Устройство ввода включает в себя блок АЦП, блок цифровой обработки и блок интерфейса.

Техническое задание

В курсовом проекте разрабатывается вычислительная система (ВС) обработки данных в реальном времени, состоящая из устройства ввода (УВ) и ПЭВМ. Входным сигналом является аналоговое напряжение. Устройство ввода включает в себя блок АЦП, блок цифровой обработки и блок интерфейса.

Назначение разработки

Курсовой проект предназначен для приобретения навыков по проектированию вычислительных систем.

Задачами курсового проекта являются:

-практическое овладение методикой проектирования вычислительной системы на основе современной элементной базы, технических средств вычислительной техники, на основе современной теории организации ЭВМ и систем;

-оценка параметров проектируемой системы и применение мер по повышению качества проектирования;

-повышение уровня конструкторского проектирования;

-приобретение практических навыков оформления и выпуска конструкторской документации в соответствии с ГОСТ.

Требования к программе или программному изделию

Требования к функциональным характеристикам

Входным сигналом устройства ввода является аналоговое напряжение, меняющегося в пределах от –2,5 до 2,5 В. Блок АЦП преобразует полученный сигнал в 10‑разрядный цифровой код. Полученный цифровой код обрабатывается в блоке цифровой обработки по следующему закону:

где Xi – текущее значение входного сигнала;

Xi-1 – предыдущее значение входного сигнала;

Yi – выходной сигнал.

Требования к составу и параметрам технических средств

На вычислительную систему и отдельные ее блоки накладываются следующие ограничения:

-конфигурация ВС: однопроцессорная система на базе микропроцессорного комплекта К1810 в минимальном режиме;

-тип применяемого АЦП параллельного действия.

Требования к информационной и программной совместимости

Связь УВ с ПЭВМ осуществляется через интерфейс системной шины. Синхронизация работы УВ и ПЭВМ осуществляется по готовности данных.

Требования к документации проекта

Курсовой проект должен быть представлен графической частью и пояснительной запиской с приложениями, содержащими конструкторскую документацию проекта. Пояснительная записка (ПЗ) оформляется согласно требованиям ЕСКД к текстовым документам и должна содержать:

1) титульный лист;

2) введение;

3) основное содержание;

4) заключение;

5) библиографический список;

6) приложения, содержащие конструкторскую документацию проекта:

Графическая часть содержит:

1) схему электрическую функциональную (Э2) устройства ввода;

2) схему электрическую принципиальную (Э3.1) устройства ввода;

3) схему электрическую принципиальную (Э3.2) блока АЦП;

4) временную диаграмму (ТЧ) работы УВ.

Стадии и этапы разработки

Работа над курсовым проектом включает следующие основные этапы:

1) Анализ технического задания и синтез варианта функциональной организации ВС;

2) Выбор элементной базы на основе анализа исходных данных;

3) Разработка алгоритма вычисления функции;

4) Разработка функциональной схемы УВ на основе синтеза функциональных схем его основных модулей;

5) Разработка принципиальных схем модулей УВ;

6) Разработка программного обеспечения УВ;

7) Получение временных диаграмм, оценивание параметров УВ и всей системы в целом;

Анализ задания

Анализ задания позволяет сделать следующие предварительные выводы:

1. Максимальная разрядность выходного значения указанной функции, в соответствии с разрядностью входных значений, равна 20, а максимальная разрядность интерфейса системной шины равна 16. Данное обстоятельство обуславливает выбрать разрядность выходного слова в 16 бит;

2. Т.к. функция содержит операцию деления, а также разрядность результата превышает разрядность системной шины, то возможны исключительные ситуации (переполнение, деление на нуль и т.п.), что требует наличие в составе УВ слов состояния и управления;

3. Небольшая номенклатура микросхем комплекта К1810 (всего 16) может потребовать применения необходимых микросхем других совместимых комплектов (например, К580);

4. Поскольку процессор должен работать в минимальном режиме, то вся вычислительная задача и задачи обмена возлагаются на него.

Выбор элементной базыБлок АЦП

Основным элементом данного блока являются микросхемы АЦП. Требуемому типу АЦП параллельного действия – соответствуют микросхемы серии К1107, причем наиболее подходящими являются микросхемы К1107ПВ3 (А, Б) и К1107ПВ4 (А, Б), являющиеся 6- и 8‑разрядными преобразователями соответственно. Т.к. собственная разрядность данных АЦП меньше требуемой, то необходимо расширение разрядности. С учетом специфики расширения разрядности данных микросхем, которая будет описана ниже, наиболее подходящей является микросхема К1107ПВ4А.

Микросхема К1107ПВ4А

Микросхема представляют собой БИС быстродействующего 8‑разрядный АЦП с ЭСЛ выходом и частотой преобразования 100 МГц. Предназначены для преобразования входного напряжения в диапазоне от –2,5 до +2,5 В в параллельный двоичный прямой код.

Преобразователь выполнен в герметичном металлокерамическом корпусе типа 2136.64–1 с вертикальным двухсторонним расположением выводов. Масса не более 22 г.

Ниже приведены основные электрические параметры.

|

Диапазон входного напряжения Uвх, В |

-2,5.. 2,5 |

|

Напряжение питания Ucc1, В Напряжение питания Ucc2, В |

5 ± 5% -5,2 ± 5% |

|

Ток потребления от источника питания Icc1, мА Ток потребления от источника питания Icc2, мА |

£ 300 £ 350 |

|

Выходное напряжение высокого уровня UOH, В Выходное напряжение низкого уровня UOL, В |

-1,1.. – 0,7 -2,0.. – 1,5 |

|

Ток потребления от ист. оп. напряжения IОП1, мА Ток потребления от ист. оп. напряжения IОП2, мА |

£ 20 £ |-20| |

| Входной ток, мА | £ 5 |

В БИС К1107ПВ4 использована типовая для класса преобразователей считывания функциональная электрическая схема. Поскольку в ней отсутствует выходной регистр, то часть периода тактирования проходит при неопределенной цифровой информации на выходе. При низком уровне тактирующего сигнала происходит выборка аналогового сигнала, на который реагируют компараторы. При подаче высокого уровня тактирующего сигнала информация с выходов компараторов переписывается в регистр, а компараторы отключаются от аналогового сигнала. Режим хранения начинается с подачи положительного фронта тактирующего импульса, но информация на цифровых выходах появляется после задержки. Период, в течение которого на цифровых выходах код не определен, равен длительности периода выборки и сдвинут во времени относительно его начала.

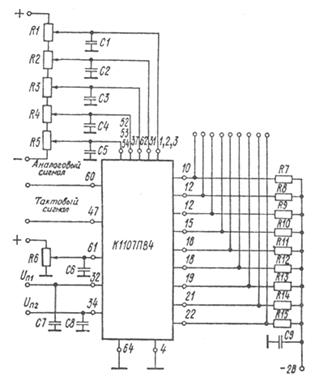

На рисунке 1 показана схема включения данной БИС и описание ее выходов [4, 6].

|

Рис. 1. Схема включения К1107ПВ4: R1…R15 = 100 Ом; C1…C9 = 1 мкФ |

1,2,3 – опорное напряжение (2,5 В); 4 – общий (цифровая земля); 5…9, 11, 14, 17, 20, 23…30, 33, 35, 38…46, 48…51, 55…59, 63 – свободные; 10 – выход переполнителя; 12 – выход 1 (старший разряд); 13 – выход 2; 15 – выход 3; 16 – выход 4; 18 – выход 5; 19 – выход 6; 21 – выход 7; 22 – выход 8 (младший разряд); 31 – вывод корректировки нелинейности Uоп3/4; 32 – напряжение питания Uп1; 34 – напряжение питания Uп2; 37 – вывод корректировки нелинейности Uоп1/4; 47 – вход (тактовый сигнал); 52,53,54 – опорное напряжение (-2,5 В); 60 – вход (аналоговый сигнал); 61 – контроль гистерезиса; 62 – вывод корректировки нелинейности Uоп1/2; 64 – общий (аналоговая земля). |

Калибровка ИС (компенсация абсолютных погрешностей в конечных точках шкалы) проводится регулировкой опорных напряжений UопXXX. Вывод 61 применяется для управления гистерезисов компараторов при подаче внешнего постоянного напряжения Uг. Для большинства случаев ИС применяются без внешнего напряжения гистерезиса, оставляя данный вывод свободным. Подача регулируемого Uг в пределах 0…2 В позволяет в небольших пределах управлять гистерезисом компараторов и рекомендуется при использовании ИС на высокой частоте для обеспечения правильной и стабильной работы АЦП.

При превышении аналоговым сигналом входного диапазона на цифровом выходе переполнения появляется напряжение высокого уровня, на остальных цифровых выходах – напряжение низкого уровня. Цифровой вывод переполнения позволяет применять параллельное соединение ИС для увеличения разрядности АЦП. Подробнее увеличение разрядности на данной БИС будет рассмотрено в следующих разделах.

Требуется предусмотреть отдельные шины «цифровая земля» и «аналоговая земля» с соединением их только в одной точке на клемме источника питания. Цифровые выходы ИС подключаются к источнику питания -2 В через резисторы сопротивлением 100 Ом.

В связи с тем, что выходные уровни сигналов не являются ТТЛ-совместимыми, то потребуется установка преобразователей уровня. Подходящим элементом является микросхема К500ПУ125 [2].

Блок цифровой обработки

Блок цифровой обработки содержит элементы, участвующие в обработке сигнала. Кроме того, данный блок выполняет инициализацию УВ, самотестирование, настройку интерфейса и т.п. Данные функции достаточно легко можно осуществить с помощью микропроцессора К1810ВМ86. Заданием предусмотрено использование данного процессора в минимальном режиме, что не допускает использования дополнительных процессоров типа АСП или СПВВ. Кроме того, для демультиплексирования шины адреса / данных в данный блок входят буферные регистры К1810ИР82 и шинные формирователи К1810ВА86. Для генерации синхроимпульсов, сигналов сброса и готовности используется БИС ГТИ К1810ГФ84.

Также неотъемлемой частью блока цифровой обработки являются микросхемы памяти. Для данного УВ необходимо ПЗУ для хранения программы и ОЗУ для хранения промежуточных результатов. Размеры необходимой памяти, а также необходимые микросхемы памяти, будут исследованы и обозначены в следующих разделах.

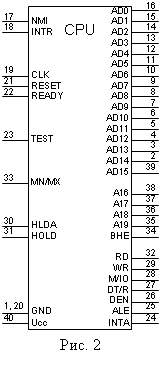

Микросхема К1810ВМ86

Микросхема представляет собой однокристальный 16‑разрядный микропроцессор, осуществляющий общую обработку данных и управление блоками системы в соответствии с заданной программой. На рисунке 2 приведено условное обозначение микросхемы с сигналами, соответствующими минимальному режиму. Подробно функционирование данной БИС описано в [3, 5, 7].

В данном проекте микропроцессор выполняет функции получения, обработки и

передачи входного сигнала в соответствии с заданной программой.

В данном проекте микропроцессор выполняет функции получения, обработки и

передачи входного сигнала в соответствии с заданной программой.

Микросхема К1810ИР82

Восьмиразрядные буферные регистр (рис. 4) используются для организации запоминающих буферов и адресных защелок. Они состоят из восьми информационных триггеров с выходными схемами с тремя состояниями, общими сигналами записи информации и управления выходными схемами.

Микросхема К1810ВА86

Восьмиразрядные шинные формирователи (рис. 5) применяют как буферные устройства шины данных. Большая выходная емкость и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи. Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления. Функциональные блоки состоят из двух усилителей формирователей с тремя состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу.

Микросхема К1810ГФ84

Генератор тактовых импульсов (рис. 3) предназначен для управления процессором и периферийными устройствами, а также для синхронизации сигналов готовности с тактовыми сигналами процессора и сигналов интерфейсной шины.

В проектируемом устройстве генератор включается независимо, т.е. выдает синхроимпульсы независимо частоты системной шины.

Блок интерфейса

Блок интерфейса предназначен для организации связи между устройством ввода и ПЭВМ, а также между процессором и блоком АЦП. Основным элементом данного блока является микросхема интерфейса. В данном случае это микросхема К580ВВ55А, представляющая собой трехпортовую БИС ввода-вывода [5]. Для подключения выходов данной БИС к системной шине необходимы буферные элементы. Их роль выполняют описанные выше элементы К1810ВА86.

Микросхема К580ВВ55А

Микросхема представляет собой универсальную программируемую БИС для организации портов ввода-вывода информации в параллельной форме. Обмен информацией между магистралью данных и микросхемой осуществляется через 8-разрядный двунаправленный тристабильный канал данных. Для связи с периферийными устройствами используются три 8-разрядных канала, в которых направление передачи информации зависит от режима работы. В нашем случае микросхема настраивается на режим 0, а порты подключаются следующим образом: порт A – блок АЦП; порт B – данные; порт C – слово управления / состояния.

Интерфейс системной шины

Подробную информацию об интерфейсе системной шины можно найти в [7]. Ниже пойдет описание, необходимое для представления принципа работы проектируемого УВ.

Для сопряжения с интерфейсом системной шины в блоке интерфейса необходима отдельная логическая схема, осуществляющая управление обращением к УВ со стороны ПЭВМ. Эта схема должна дешифрировать адрес и управляющие сигналы на системной шине и в соответствии с ними выдавать управляющие сигналы обратно на системную шину и в УВ. К сигналам выдаваемым на системную шину относится сигнал IO16, говорящий о 16-разрядной передаче данных. Данный сигнал будет иметь активный (низкий) уровень в случае выдачи на шину данных результата. В случаях чтения слова состояния или записи управляющего слова данный сигнал имеет высокий уровень, что говорит о передаче байта. К сигналам, выдаваемым в УВ, относятся сигналы управления шинными формирователями на выходах портов и сигнал готовности на ГТИ, приостанавливающий работу процессора ВМ86 на время обмена, а также сигнал, информирующий процессор о том, что данные еще не были считаны и нет необходимости формировать следующий результат. Приостановка процессора необходима для избежания коллизий.

Для обращения к проектируемому устройству резервируются адреса: 320h – для чтения результата; 322h для чтения слова состояния и для записи управляющего слова.

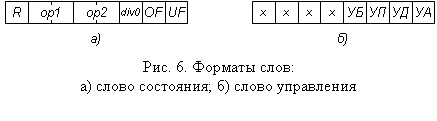

Ниже приведены форматы слова состояния и слова управления:

Слово состояния:

R – флаг готовности результат. Устанавливается в 1 после записи в выходной регистр результата и сбрасывается в 0 при чтении регистра. Анализируется процессором для записи нового результата только после чтения предыдущего, и приложением работы с УВ, для чтения результата только после его готовности.

op1, op2 – значение операндов, участвующих в вычислении функции: текущее значения (op1) и предыдущее (op2). Могут принимать значения: 0x – произвольное ненулевое число; 10 – нуль; 11 – бесконечность. Предназначены для выявления исключительных ситуаций, таких как 0/0 или ¥/¥. В таких ситуациях выдается нулевой результат, а эти биты должны быть проанализированы для определения типа ситуации.

div0, OF, UF – флаги ошибок деления на нуль, переполнения и антипереполнения соответственно.

Слово управления:

УБ управление бесконечностью. В случаях, когда результатом является бесконечность, данный бит управляет формированием результата. 0 – выдается нулевое значение результата; 1 – выдается максимально возможное значение (0FFFFh). В обоих случаях определить бесконечность можно анализом слова состояния.

УП управление переполнением. В случаях, когда результат превышает 16‑разрядов, данный бит управляет формированием результата: 0 – результатом будут младшие 16 бит результата; 1 – результатом будет максимально возможное значение (0FFFFh). В обоих случаях установить факт переполнения можно анализом слова состояния.

УД управление данными АЦП. В случаях, когда разряд переполнения АЦП установлен в 1, данный бит позволяет определить как интерпретировать входной сигнал: 0 сходной сигнал интерпретируется как бесконечность; 1 – входной сигнал интерпретируется как максимально возможное значение (0FFFFh).

УА управление антипереполнением. Антипереполнение возникает в случае, когда значение результата оказывается меньше младшего разряда. Данный бит позволяет интерпретировать данный результат двумя способами: 0 – нулевой результат; 1 результат равен 1.

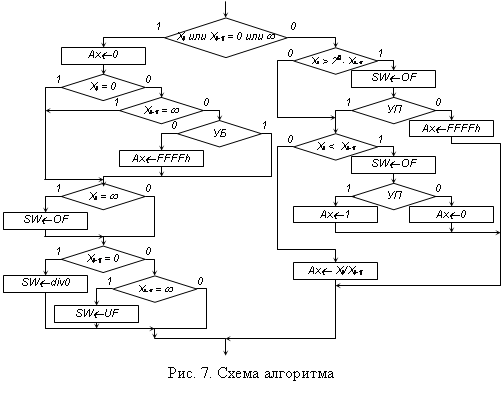

Алгоритм вычисления функции

Вычисляемая в устройстве ввода функция имеет вид:

где Xi – текущее значение входного сигнала;

Xi-1 – предыдущее значение входного сигнала;

Yi – выходной сигнал.

Разрядность входного сигнала равна 10, в связи с чем максимальная разрядность результата будет составлять 20. Однако, из-за особенностей работы УВ и используемой аппаратуры, результат формируется 16-разрядным.

Возможны два варианта вычисления указанной функции, отличающиеся последовательностью выполняемых операций: 1) деление, возведение в квадрат; 2) возведение в квадрат, деление. Первый вариант предпочтительнее, т. к. обладает меньшей вычислительной сложностью, однако при его реализации необходимо учесть, что остаток от первоначального деления также должен участвовать в последующем возведении в квадрат.

На рисунке 7 приведен фрагмент алгоритма вычисления функции и формирования результата. При этом следует обратить внимание на некоторые особенности алгоритма. Входные значения находятся регистрах Ax=Xi и Bx=Xi-1. Результат формируется в регистре Ax. Т.к. слово состояния представляет собой набор бит, то операция типа SW¬div0 представляет собой установка соответствующего бита. Более того, наличие исключительных ситуаций предполагает наличия двух значений для каждого операнда: само значение и его представление в слове состояния (см. рисунок 6), причем, изменение одного из них не влечет изменения другого.

Ниже приведена программа, соответствующая приведенному

|

алгоритму:

test Cl, 01010000b ; будут ли исключительные ситуации?

jnz @@LABEL3 ; будут – переход

mov Dx, Ax

shr Dx, 8

cmp Dx, Bx ; X(i)>=256*X (i‑1)?

jae @@LABEL8

@@LABEL9:

cmp Ax, Bx ; X(i)<X (i‑1)?

jl @@LABEL10

xor Dx, Dx ; очистим Dx

div Bx ; Dx: Ax/Bx -> A+D/B

mov Si, Ax ; сохраним значение A

mul Dx ; Dx: Ax < – A*D

shl Ax, 1 ; *2

shl Dx, 1

div Bx ; 2*A*D/B

mov Bx, Ax

mov Ax, Si ; восстановим A

mul Ax ; Dx: Ax < – A*A

add Ax, Bx ; в Ax – результат!

jmp @@LABEL7

@@LABEL8:

or Cl, 00000010b ; SW < – OF

test Ch, 00000100b ; переполнение. Что делать?

jnz @@LABEL9

mov Ax, 0FFFFh ; результат < – максимум

jmp @@LABEL7

@@LABEL10:

or Cl, 00000001b ; SW < – UF

mov Al, Ch

and Ax, 0001h ; результат < – UF

jmp @@LABEL7

@@LABEL3:

xor Ax, Ax ; результатом будет 0

mov Dl, Cl ; Dl < – SW

mov Dh, Cl ; Dh < – SW

and Dx, 0001100001100000b ; замаскируем по операндам

cmp Dl, 01000000b ; X(i)==0?

je @@LABEL4 ; да – на выход

cmp Dh, 00011000b ; X (i‑1)==бесконечность?

je @@LABEL4 ; да – на выход

test Ch, 00001000b ; результат = бесконечность

jnz @@LABEL4

mov Ax, 0FFFFh ; результат < – максимум

@@LABEL4:

cmp Dl, 01100000b ; X(i)==бесконечность?

jne @@LABEL5

or Cl, 00000010b ; SW < – OF

@@LABEL5:

cmp Dh, 00010000b ; X (i‑1)==0?

jne @@LABEL6

or Cl, 00000100b ; SW < – div0

@@LABEL6:

cmp Dh, 00011000b ; X (i‑1)==бесконечность?

jne @@LABEL7

or Cl, 00000001b ; SW < – UF

@@LABEL7:

Полный текст программы работы процессора с учетом самотестирования, настройки интерфейса и вычисления функции приведен в приложении А.

Размер всей программы составляет 226 байт, что позволяет ограничиться размером ПЗУ в 1 Кбайт (512К´16). Организовать такую память можно путем параллельного подключения двух микросхем КМ1608РТ2 [5]. Более того, данная программа не требует сохранения промежуточных результатов в памяти, что позволяет исключить из состава устройства ОЗУ.

Разработка функциональной схемы УВ

Рассмотрим функциональную схему УВ раздельно по ее блокам.

Блок АЦП

Функциональная схема данного блока является достаточно простой. Она представляет собой набор АЦП, цифровые выходы которых подключены к порту A блока интерфейса через специальный разъем.

Блок цифровой обработки

Блок цифровой обработки состоит из: микропроцессора, буферных регистров, шинных формирователей, генератора тактовых импульсов, микросхем памяти и дешифратора управляющих сигналов, объединенных для организации однопроцессорной системы [7].

Буферные регистры и шинные формирователи необходимы для демультиплексирования шин адреса и данных. Генератор тактовых импульсов формирует тактовые импульсы, сигналы сброса и готовности. Дешифратор управляющих сигналов декодирует сигналы управления процессора и вырабатывает сигналы чтения и записи памяти и внешних устройств (портов).

Элементы соединены для организации однопроцессорной системы с памятью и портами ввода-вывода.

Блок интерфейса

Блок интерфейса состоит из: микросхемы интерфейса, шинных формирователей и буферных регистров (для подключения к системной шине), логики управления системной шиной, дешифратора системного адреса и логики управления готовностью и чтением результата.

Логика управления системной шиной заключается в выдаче сигнала IO16, информирующего о передаче 16‑разрядных данных.

Дешифратор системного адреса необходим для определения факта обращения к УВ со стороны ПЭВМ. Для обращения к проектируемому устройству зарезервированы два адреса, на которые оно будет откликаться: 320h – для чтения результата и 322h – для чтения слова состояния и для записи управляющего слова.

Логика управления готовностью и чтением результата предназначена для исключения ситуаций, когда процессор подготовил новые данные, а предыдущие еще не были считаны. Данная операция осуществляется путем подачи на вход TEST процессора сигнала неготовности на время, пока результат не будет считан. Процессор ждет разрешающего уровня на данном входе, а затем приступает к формированию следующего результата.

Функциональная схема проектируемого УВ приведена на отдельном чертеже К2.006.223.Э2.

Разработка принципиальной схемы УВБлок АЦП

Блок АЦП конструктивно разрабатывается как отдельный модуль, подключаемый к устройству через специальный разъем типа RS‑232.

Выбранный тип микросхемы АЦП К1107ПВ4 имеет ряд особенностей. Выходные уровни данной микросхемы соответствуют ЭСЛ логике, что требует наличия преобразователей уровня для подключения к устройству. В качестве преобразователей уровня используется микросхема К500ПУ125.

Кроме того, микросхема АЦП имеет напряжение питания –5,2 В, что требует подключения стабилизатора напряжения. В данном случае это стабилизатор напряжения отрицательной полярности К142ЕН10. С помощью такого же элемента формируется напряжение –2 В, необходимое для подключения цифровых выводов микросхем через сопротивления 100 Ом.

Регулировка напряжения гистерезиса отсутствует в связи с тем, работа микросхем АЦП будет производиться на малых частотах (5 МГц).

Входное напряжение подается в модуль через специальный разъем типа 3.5 mm Mono Telephone plug. Аналоговая земля соединяется с цифровой землей.

Схема электрическая принципиальная блока АЦП приведена на отдельном чертеже К2.006.223.Э3.2.

Блок цифровой обработки

Основным элементом данного блока является микропроцессор К1810ВМ86, на вход MN/MX которого подается напряжение высокого уровня, что соответствует минимальному режиму. Входы CLK, RESET и READY подключены к ГТИ. Выходы BHE, AD0‑AD15 демультиплексируются с помощью буферных регистров и шинных формирователей и образуют шину адреса и шину данных. Выходы M/IO, WR и RD используются для формирования сигналов управления памятью и внешними устройствами (портами). Выходы NMI, INT, INTA, HOLD и HLDA не используются за ненадобностью.

Генератор тактовых импульсов К1810ГФ84 формирует собственные синхроимпульсы, для чего к его входам X1 и X2 подключен кварцевый резонатор, а к входу TANK – RC‑цепочка. Сигнал RES на вход ГТИ подается с системной шины. На вход RDY подается сигнал от схемы управления системной шиной (см. блок интерфейса), предназначенный для запрещения работы на время обращения к УВ со стороны ПЭВМ. Это необходимо для избежания коллизий одновременного доступа к портам ввода-вывода.

Для организации памяти используются микросхемы КМ1608РТ2. В процессе работы процессор будет обращаться лишь к самому старшему 1 Кбайту памяти и к небольшому числу портов. Данный факт позволяет в рамках курсового проекта сократить разрядность шины адреса до 10 при обращении к памяти и до 4 при обращении к портам, что позволяет заметно сократить аппаратные затраты и уменьшить сложность устройства.

Блок интерфейса

Микросхема параллельного интерфейса К580ВВ55 позволяет подключать к ней до трех 8‑разрядных внешних устройств (портов). Для организации 16‑разрядных портов параллельно устанавливаются две такие микросхемы. К порту A обеих микросхем подключается блок АЦП. Порт B подключен к системной шине и используется для выдачи результат. Порт C первой микросхемы используется для выдачи на системную шину слова состояния, а порт C второй микросхемы используется для приема слова управления.

Также, важными частями блока интерфейса является логика чтения результата и логика управления системной шиной.

Логика управления готовностью и чтением результата предназначена для исключения ситуаций, когда процессор подготовил новые данные, а предыдущие еще не были считаны. Данная операция осуществляется путем подачи на вход TEST процессора сигнала неготовности на время, пока результат не будет считан. Процессор ждет разрешающего уровня на данном входе, а затем приступает к формированию следующего результата. Аппаратно логика реализована на одном D‑триггере, устанавливающимся в 1 при записи результата в порт и сбрасывающимся в 0 при чтении из порта. Выход данного триггера соединен с входом TEST процессора.

Логика управления системной шиной заключается в выдаче сигнала IO16, информирующего о передаче 16‑разрядных данных. Также, данная логика формирует управляющие сигналы, отпирающие необходимые буферы на входах и выходах портов, а также сигнал RDY на ГТИ, запрещающий вырабатывать синхроимпульсу на время обращения со стороны системной шины.

Факт обращения со стороны системной шины определяется с помощью дешифратора системного адреса. Для обращения к проектируемому устройству зарезервированы два адреса, на которые оно будет откликаться: 320h – для чтения результата и 322h – для чтения слова состояния и для записи управляющего слова.

Принципиальная схема проектируемого устройства приведена на чертеже К2.006.223.Э3.1.

Разработка программного обеспечения УВ

При разработке программного обеспечения УВ следует читывать следующие детали. Устройство реагирует только на два адреса: 320h – данные и 322h – управляющее слово (для записи) и слово состояния (для чтения). В связи с особенностями построения УВ при работе со словами управления и состояния необходимо использовать младший байт данных системной шины.

Старший бит слова состояния установленный в 1 информирует о готовности нового результата. В противном случае, с порта данных можно прочитать старое значение. Более того, если результат оказался нулевым, то это может означать исключительную ситуацию или бесконечность. В этом случае для определения действительного результата следует проводить анализ слова состояния.

Ниже приведен фрагмент программы для работы с проектируемым устройством. Программа «вешает» процедуру чтения и обработки сигнала на прерывание от таймера. Полученные результаты записываются в некоторый файл. В случае если устройство не исправно, в файл будет записано соответствующее сообщение, а вектор прерывания не будет перегружен.

386

portDAT EQU 0320h

portCW EQU 0322h

portSW EQU 0322h

S_STACK SEGMENT PARA STACK 'stack'

DB 32 DUP('stack')

S_STACK ENDS

S_DAT SEGMENT PARA PUBLIC 'data'

msgErrDevice label dword

db 'Устройство сломано!'

outData dd ?

FName label dword

db 'output.dat', 0

FHandler dw ?

oldVect label dword

oldIp dw ?

oldCs dw ?

IntVect dd Int8

S_DAT ENDS

PRG_COD SEGMENT PARA PUBLIC 'code'

ASSUME CS:PRG_COD, DS:S_DAT, SS:S_STACK

Int8 PROC FAR ; модуль перегруженного прерывания

pusha ; сохраним все регистры

in Al, portSW ; читаем SW

test Al, 10000000b ; результат готов?

jz @@EXIT ; нет на выход

in Ax, portDAT ; читаем результат

cmp Ax, 0 ; исключительная ситуация

jne @NO_EXEPTION ; нет переход

; обработка исключения (может отсутствовать)

;…

@NO_EXEPTION:

mov word ptr [outData], Ax ; сохраним результат в файле

mov Ah, 40h

mov Bx, Ds:FHandler

mov Cx, 2

lds Dx, outData

int 21h

@@EXIT:

popa ; восстановим регистры

iret

Int8 ENDP

SetInt8 PROC

pusha

mov Ax, 3508h ; сохраним старый вектор прерывания

int 21h

mov oldIp, Bx

mov Ax, Es

mov oldCs, Ax

lds Dx, IntVect

mov Ax, 2508h ; установим новый

int 21h

popa

ret

SetInt8 ENDP

MAIN PROC FAR

pusha

mov Ah, 3Ch ; создадим файл

mov Cx, 0020h

lds Dx, FName

int 21h

jc @ERROR ; ошибка?

mov Ds:FHandler, Ax ; сохраним хэндлер

in Al, portSW ; читаем SW

cmp Al, 0FFh ; ошибка в устройстве?

jne @DEVICE_OK ; нет – переход

mov Ah, 40h ; запишем в выходной файл

mov Bx, Ds:FHandler ; сообщение об ошибке

mov Cx, 20

lds Dx, msgErrDevice

int 21h

mov Ah, 3Eh ; закроем файл

int 21h

jmp @ERROR ; на выход

@DEVICE_OK:

mov Al, 00000011b

out portCW, Al ; запишем CW

call SetInt8 ; «посадим» на прерывание от таймера

@ERROR:

popa

ret

MAIN ENDP

PRG_COD ENDS

END MAIN

Параметры системы1. Максимальная частота работы системы:

fmax=5 МГц

2. Максимальное время задержки выходных данных:

TЗД=727×tCLK=145 мкс

3. потребляемая мощность:

не более 15 Вт

4. надежность устройства (l=10-7 час-1):

P(10000)=e-25×l×t= 0,98

Конструктивно УВ может быть выполнено на двух печатных платах. На первой будут размещаться блок цифровой обработки и блок интерфейса, на второй – блок АЦП. Подключение к ПЭВМ осуществляется посредством разъема тип EISA. Подключение блока АЦП к устройству – посредством разъема RS‑232 (или другого).

Временная диаграмма работы устройства ввода приведена на чертеже К2.006.223.ТЧ.

Заключение

В ходе работы над курсовым проектом по курсу «Организация ЭВМ комплексов и систем» было разработано устройство ввода, предназначенное для автоматического ввода и цифровой обработки аналогового сигнала. Были разработаны модули, входящие в состав устройства ввода, а также программное обеспечение самого УВ и для совместной работы его в ПЭВМ. Были оценены параметры вычислительной системы, выбран оптимальный вариант схемы. В соответствии со всеми этапами проекта были оформлены соответствующие чертежи и документация.

Список использованной литературы

1. Компьютерное оформление отчетных документов: методические указания / Составитель Т.И. Матикашвили; ТулГУ. Тула, 2000. – 36 с.

2. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах: Cправочник. – М.: Радио и связь, 1990. – 304 c

3. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник в 2-х томах под ред. В.А. Шахнова.

4. Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник. Т. 8. - М.: ИП РадиоСофт, 2000

5. Цифровые и аналоговые интегральные микросхемы: Справочник / Под ред. С.В. Якубовского. М., 1990

6. Телец В.А., Федорков Б.Г. Микросхемы ЦАП и АЦП: Функционирование, параметры, применения. – М.: Энергоатом, 1998

7. Казаринов Ю.М. и др. Микропроцессорный комплект К1810: Структура, программирование, применение. – М.: Высш. шк., 1990

Приложение А. Текст программы работы УВ

SegRAM EQU 0FC00h ; сегмент ПЗУ

PrgSize EQU 112 ; размер программы (в словах)

portDAC EQU 0000b ; порт АЦП

portDAT EQU 0001b ; порт данных

portCW EQU 0110b ; порт упр. слова (CW)

portSW EQU 1010b ; порт слова сост. (SW)

portPRG EQU 0011b ; порт УС микросхем интерфейса

CODE

STARTUP

; тест ПЗУ

mov Ax, SegRAM

mov Ds, Ax ; в Ds – сегмент ПЗУ

xor Ax, Ax ; очистим Ax

mov Cx, PrgSize ; в Cx – размер программы (в словах)

xor Bx, Bx

@@LOOP1:

add Ax, Ds: [Bx] ; в Ax – сумма всех слов

add Bx, 2

loop @@LOOP1

cmp Ax, Ds: [PrgSize*2] ; совпадает ли с заданным?

je @CONTINUE1 ; да – идем дальше

mov Al, 0FFh

out portSW, Al ; SW < – ошибка

@HALT:

hlt ; вешаем систему

jmp @HALT

@CONTINUE1:

; программирование интерфейса

mov Al, 10010000b ; первая МС. порт C на ввод

mov Ah, 10011001b ; вторая МС. порт C на вывод

out portPRG, Ax ; программируем

; выполнение функции

mov Bx, 1 ; по-умолчанию X(0)=1

xor Cx, Cx ; очистим Cl=SW и Ch=CW

@@LOOP2:

xchg Ax, Cx

out portSW, Al ; SW < – данные не готовы

xchg Ax, Cx

and Cl, 01100000b

shr Cl, 2

in Ax, portCW ; в Ch – слово управления

mov Ch, Ah

in Ax, portDAC ; в Ax – с АЦП

test Ax, 0400h ; было переполнение?

jz @@LABEL1 ; не было – приступим к работе

test Ch, 00000010b ; переполнение. Что делать?

jz @@LABEL2

or Cl, 01100000b ; установим в бесконечность

@@LABEL2:

mov Ax, 0FFFFh ; установим максимум

@@LABEL1:

test Cl, 01010000b ; будут ли исключительные ситуации?

jnz @@LABEL3 ; будут -> переход

mov Dx, Ax

shr Dx, 8

cmp Dx, Bx ; X(i)>=256*X (i‑1)?

jae @@LABEL8

@@LABEL9:

cmp Ax, Bx ; X(i)<X (i‑1)?

jl @@LABEL10

xor Dx, Dx ; очистим Dx

div Bx ; Dx: Ax/Bx -> A+D/B

mov Si, Ax ; сохраним значение A

mul Dx ; Dx: Ax < – A*D

shl Ax, 1 ; *2

shl Dx, 1

div Bx ; 2*A*D/B

mov Bx, Ax

mov Ax, Si ; восстановим A

mul Ax ; Dx: Ax < – A*A

add Ax, Bx ; в Ax – результат!

jmp @@LABEL7

@@LABEL8:

or Cl, 00000010b ; SW < – OF

test Ch, 00000100b ; переполнение. Что делать?

jnz @@LABEL9

mov Ax, 0FFFFh ; результат < – максимум

jmp @@LABEL7

@@LABEL10:

or Cl, 00000001b ; SW < – UF

mov Al, Ch

and Ax, 0001h ; результат < – UF

jmp @@LABEL7

@@LABEL3:

xor Ax, Ax ; результатом будет 0

mov Dl, Cl ; Dl < – SW

mov Dh, Cl ; Dh < – SW

and Dx, 0001100001100000b ; замаскируем по операндам

cmp Dl, 01000000b ; X(i)==0?

je @@LABEL4 ; да – на выход

cmp Dh, 00011000b ; X (i‑1)==бесконечность?

je @@LABEL4 ; да – на выход

test Ch, 00001000b ; результат = бесконечность

jnz @@LABEL4

mov Ax, 0FFFFh ; результат < – максимум

@@LABEL4:

cmp Dl, 01100000b ; X(i)==бесконечность?

jne @@LABEL5

or Cl, 00000010b ; SW < – OF

@@LABEL5:

cmp Dh, 00010000b ; X (i‑1)==0?

jne @@LABEL6

or Cl, 00000100b ; SW < – div0

@@LABEL6:

cmp Dh, 00011000b ; X (i‑1)==бесконечность?

jne @@LABEL7

or Cl, 00000001b ; SW < – UF

@@LABEL7:

out portDAT, Ax ; результат в порт

mov Bx, Ax ; X (i‑1)=X(i)

mov Al, Cl

or Al, 10000000b ; SW < – данные готовы!

out portSW, Al ; SW в порт

wait ; ждем пока данные прочитают

jmp @@LOOP2 ; в начало

db 00h ; выравниевание на границу слова

dw xxxxh ; контрольная сумма ПЗУ

END

Также, при программировании ПЗУ необходимо записать команду перехода jmp 0FC00:0000h по адресу ПЗУ 3F0h (физический адрес 0FFF0h).

© 2010 Интернет База Рефератов