Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Курсовая работа: Классификация и структура микроконтроллеров

Курсовая работа: Классификация и структура микроконтроллеров

Содержание

Введение

1. Общая часть

1.1 Классификация и структура микроконтроллеров

1.2 Структура процессорного ядра микроконтроллеров

2. Специальная часть

2.1 CISC и RISC архитектура процессора

2.2 RISC- архитектура

2.3 Микроконтроллер с RISC архитектурой

Заключение

Список используемой литературы

Введение

Микроконтроллер (MCU) микросхема, предназначенная для управления электронными устройствами. Типичный микроконтроллер сочетает в себе функции процессора и периферийных устройств, может содержать ОЗУ и ПЗУ. По сути, это однокристальный компьютер, способный выполнять простые задачи. Использование одной микросхемы, вместо целого набора, как в случае обычных процессоров, применяемых в персональных компьютерах, значительно снижает размеры, энергопотребление и стоимость устройств, построенных на базе микроконтроллеров. Микроконтроллеры являются основой для построения встраиваемых систем, их можно встретить во многих современных приборах, таких, как телефоны, стиральные машины и т. п. Термин «микроконтроллер» (МК) вытеснил из употребления ранее использовавшийся термин «однокристальная микро-ЭВМ». Первый же патент на однокристальную микро-ЭВМ был выдан в 1971 году инженерам М. Кочрену и Г. Буну, сотрудникам Texas Instruments. Именно они предложили на одном кристалле разместить не только микропроцессор, но и память, устройства ввода-вывода. С появлением однокристальных микро-ЭВМ связывают начало эры компьютерной автоматизации в области управления. По-видимому, это обстоятельство и определило термин «микроконтроллер» (control — управление). В 1979 году НИИ ТТ разработали однокристальную 16-разрядную ЭВМ К1801ВЕ1, архитектура которой называлась «Электроника НЦ». В 1980 году фирма Intel выпускает микроконтроллер i8048. Чуть позже в этом же году Intel выпускает следующий микроконтроллер: i8051. Удачный набор периферийных устройств, возможность гибкого выбора внешней или внутренней программной памяти и приемлемая цена обеспечили этому микроконтроллеру успех на рынке. С точки зрения технологии микроконтроллер i8051 являлся для своего времени очень сложным изделием — в кристалле было использовано 128 тыс. транзисторов, что в 4 раза превышало количество транзисторов в 16-разрядном микропроцессоре i8086.

На сегодняшний день существует более 200 модификаций микроконтроллеров, совместимых с I8051, выпускаемых двумя десятками компаний, и большое количество микроконтроллеров других типов. Популярностью у разработчиков пользуются 8-битные микроконтроллеры PIC фирмы Microchip Technology и AVR фирмы Atmel, шестнадцатибитные MSP430 фирмы TI, а также ARM, архитектуру которых разрабатывает фирма ARM и продаёт лицензии другим фирмам для их производства, процессоров — микроконтроллеры.

При проектировании микроконтроллеров приходится соблюдать баланс между размерами и стоимостью с одной стороны и гибкостью и производительностью с другой. Для разных приложений оптимальное соотношение этих и других параметров может различаться очень сильно. Поэтому существует огромное количество типов микроконтроллеров, отличающихся архитектурой процессорного модуля, размером и типом встроенной памяти, набором периферийных устройств, типом корпуса и т. д.

1. Общая часть

1.1 Классификация и структура микроконтроллеров

В настоящее время выпускается целый ряд типов МК. Все эти приборы можно условно разделить на три основных класса:

- 8-разрядные МК для встраиваемых приложений;

- 16- и 32-разрядные МК;

- цифровые сигнальные процессоры (DSP).

Наиболее распространенным представителем семейства МК являются 8-разрядные приборы, широко используемые в промышленности, бытовой и компьютерной технике. Они прошли в своем развитии путь от простейших приборов с относительно слаборазвитой периферией до современных многофункциональных контроллеров, обеспечивающих реализацию сложных алгоритмов управления в реальном масштабе времени. Причиной жизнеспособности 8-разрядных МК является использование их для управления реальными объектами, где применяются, в основном, алгоритмы с преобладанием логических операций, скорость обработки которых практически не зависит от разрядности процессора.

Росту популярности 8-разрядных МК способствует постоянное расширение номенклатуры изделий, выпускаемых такими известными фирмами, как Motorola, Microchip, Intel, Zilog, Atmel и многими другими. Современные 8-разрядные МК обладают, как правило, рядом отличительных признаков. Перечислим основные из них:

- модульная организация, при которой на базе одного процессорного ядра (центрального процессора) проектируется ряд (линейка) МК, различающихся объемом и типом памяти программ, объемом памяти данных, набором периферийных модулей, частотой синхронизации;

- использование закрытой архитектуры МК, которая характеризуется отсутствием линий магистралей адреса и данных на выводах корпуса МК. Таким образом, МК представляет собой законченную систему обработки данных, наращивание возможностей которой с использованием параллельных магистралей адреса и данных не предполагается;

- использование типовых функциональных периферийных модулей (таймеры, процессоры событий, контроллеры последовательных интерфейсов, аналого-цифровые преобразователи и др.), имеющих незначительные отличия в алгоритмах работы в МК различных производителей;

- расширение числа режимов работы периферийных модулей, которые задаются в процессе инициализации регистров специальных функций МК.

При модульном принципе построения все МК одного семейства содержат процессорное ядро, одинаковое для всех МК данного семейства, и изменяемый функциональный блок, который отличает МК разных моделей. Процессорное ядро включает в себя:

- центральный процессор;

- внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления;

- схему синхронизации МК;

- схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса) и т.д.

Изменяемый функциональный блок включает в себя модули памяти различного типа и объема, порты ввода/вывода, модули тактовых генераторов (Г), таймеры. В относительно простых МК модуль обработки прерываний входит в состав процессорного ядра. В более сложных МК он представляет собой отдельный модуль с развитыми возможностями. В состав изменяемого функционального блока могут входить и такие дополнительные модули как компараторы напряжения, аналого-цифровые преобразователи (АЦП) и другие. Каждый модуль проектируется для работы в составе МК с учетом протокола ВКМ. Данный подход позволяет создавать разнообразные по структуре МК в пределах одного семейства.

1.2 Структура процессорного ядра микроконтроллера

Основными характеристиками, определяющими производительность процессорного ядра МК, являются:

- набор регистров для хранения промежуточных данных;

- система команд процессора;

- способы адресации операндов в пространстве памяти;

- организация процессов выборки и исполнения команды.

С точки зрения системы команд и способов адресации операндов процессорное ядро современных 8-разрядных МК реализует один из двух принципов построения процессоров:

- процессоры с CISC-архитектурой, реализующие так называемую полную систему команд (Complicated Instruction Set Computer);

- процессоры с RISC-архитектурой, реализующие сокращенную систему команд (Reduced Instruction Set Computer).

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК процессор с CISC-архитектурой может иметь однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. Время выполнения команды может составлять от 1 до 12 циклов. К МК с CISC-архитектурой относятся МК фирмы Intel с ядром MCS-51, которые поддерживаются в настоящее время целым рядом производителей, МК семейств НС05, НС08 и НС11 фирмы Motorola и ряд других.

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК PIC16 и PIC17 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

С точки зрения организации процессов выборки и исполнения команды в современных 8-разрядных МК применяется одна из двух уже упоминавшихся архитектур МПС: фон-неймановская (принстонская) или гарвардская.

Основное преимущество архитектуры Фон-Неймана – упрощение устройства МПС, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МПС с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтому фон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации операндов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению.

В настоящее время наиболее яркими представителями микроконтроллеров SISC и RISC, имеющих соответственно фон-неймановскую и гарвардскую архитектуры являются микроконтроллеры i8051 и AVR – микроконтроллеры фирмы Atmel, которые по ряду характеристик превзошли очень известные PIC – микроконтроллеры. Поэтому рассмотрим организацию и устройство вышеперечисленных представителей.

2. Специальная часть

2.1 CISC и RISC архитектура процессора

Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники, являются архитектуры CISC и RISC. Основоположником CISC-архитектуры архитектуры с полным набором команд (CISC – Complete Instruction Set Computer) можно считать фирму IBM с ее базовой архитектурой IBM/360, ядро которой используется с 1964 г. и дошло до наших дней, например, в таких современных мейнфреймах, как IBM ES/9000.

Лидером в разработке микропроцессоров с полным набором команд считается компания Intel с микропроцессорами X86 и Pentium. Это практически стандарт для рынка микропроцессоров.

Простота архитектуры RISC-процессора обеспечивает его компактность, практическое отсутствие проблем с охлаждением кристалла, чего нет в процессорах фирмы Intel, упорно придерживающейся пути развития архитектуры CISC. Формирование стратегии CISC-архитектуры произошло за счет технологической возможности перенесения "центра тяжести" обработки данных с программного уровня системы на аппаратный, так как основной путь повышения эффективности для CISC-компьютера виделся, в первую очередь, в упрощении компиляторов и минимизации исполняемого модуля. На сегодняшний день CISC-процессоры почти монопольно занимают на компьютерном рынке сектор персональных компьютеров, однако RISC-процессорам нет равных в секторе высокопроизводительных серверов и рабочих станций.

Основные черты RISC-архитектуры с аналогичными по характеру чертами CISC-архитектуры отображаются следующим образом (табл.1):

Таблица 1.Основные черты архитектуры

| CISC- архитектура | RISC-архитектура |

| Многобайтовые команды | Однобайтовые команды |

| Малое количество регистров | Большое количество регистров |

| Сложные команды | Простые команды |

| Одна или менее команд за один цикл процессора | Несколько команд за один цикл процессора |

| Традиционно одно исполнительное устройство | Несколько исполнительных устройств |

Одним из важных преимуществ RISC-архитектуры является высокая скорость арифметических вычислений. RISC-процессоры первыми достигли планки наиболее распространенного стандарта IEEE 754, устанавливающего 32-разрядный формат для представления чисел с фиксированной точкой и 64-разрядный формат "полной точности" для чисел с плавающей точкой. Высокая скорость выполнения арифметических операций в сочетании с высокой точностью вычислений обеспечивает RISC-процессорам безусловное лидерство по быстродействию в сравнении с CISC-процессорами.

Другой особенностью RISC-процессоров является комплекс средств, обеспечивающих безостановочную работу арифметических устройств: механизм динамического прогнозирования ветвлений, большое количество оперативных регистров, многоуровневая встроенная кэш-память.

Организация регистровой структуры – основное достоинство и основная проблема RISC. Практически любая реализация RISC-архитектуры использует трехместные операции обработки, в которых результат и два операнда имеют самостоятельную адресацию – R1 : = R2, R3. Это позволяет без существенных затрат времени выбрать операнды из адресуемых оперативных регистров и записать в регистр результат операции. Кроме того, трехместные операции дают компилятору большую гибкость по сравнению с типовыми двухместными операциями формата "регистр – память" архитектуры CISC. В сочетании с быстродействующей арифметикой RISC-операции типа "регистр – регистр" становятся очень мощным средством повышения производительности процессора.

Вместе с тем опора на регистры является ахиллесовой пятой RISC-архитектуры. Проблема в том, что в процессе выполнения задачи RISC-система неоднократно вынуждена обновлять содержимое регистров процессора, причем за минимальное время, чтобы не вызывать длительных простоев арифметического устройства. Для CISC-систем подобной проблемы не существует, поскольку модификация регистров может происходить на фоне обработки команд формата "память – память".

Существуют два подхода к решению проблемы модификации регистров в RISC-архитектуре: аппаратный, предложенный в проектах RISC-1 и RISC-2, и программный, разработанный специалистами IВМ и Стэндфордского университета. Принципиальная разница между ними заключается в том, что аппаратное решение основано на стремлении уменьшить время вызова процедур за счет установки дополнительного оборудования процессора, тогда как программное решение базируется на возможностях компилятора и является более экономичным с точки зрения аппаратуры процессора.

2.2 RISC-архитектура

В 70-е годы XX века ученые выдвинули революционную по тем временам идею создания микропроцессора, "понимающего" только минимально возможное количество команд.

Замысел RISC- процессора (Reduced Instruction Set Computer, компьютер с сокращенным набором команд) родился в результате практических исследований частоты использования команд программистами, проведенных в 70-х годах в США и Англии. Их непосредственный итог - известное "правило 80/20": в 80% кода типичной прикладной программы используется лишь 20% простейших машинных команд из всего доступного набора.

Первый "настоящий" RISC-процессор с 31 командой был создан под руководством Дэвида Паттерсона из Университета Беркли, затем последовал процессор с набором из 39 команд. Они включали в себя 20-50 тыс. транзисторов. Плодами трудов Паттерсона воспользовалась компания Sun Microsystems, разработавшая архитектуру SPARC с 75 командами в конце 70-х годов. В 1981 г. в Станфордском университете стартовал проект MIPS по выпуску RISC-процессора с 39 командами. В итоге была основана корпорация Mips Computer в середине 80-х годов и сконструирован следующий процессор уже с 74 командами.

По данным независимой компании IDC, в 1992 году архитектура SPARC занимала 56% рынка, далее следовали MIPS - 15% и PA-RISC - 12,2%

Примерно в то же время Intel разработала серию 80386, последних "истинных" CISC-процессоров в семействе IA-32. В последний раз повышение производительности было достигнуто только за счет усложнения архитектуры процессора: из 16-разрядной она превратилась в 32-разрядную, дополнительные аппаратные компоненты поддерживали виртуальную память, и добавился целый ряд новых команд.

Основные особенности RISC-процессоров:

ü Сокращенный набор команд (от 80 до 150 команд).

ü Большинство команд выполняется за 1 такт.

ü Большое количество регистров общего назначения.

ü Наличие жестких многоступенчатых конвейеров.

ü Все команды имеют простой формат, и используются немногие способы адресации.

ü Наличие вместительной раздельной кэш-памяти.

ü Применение оптимизирующих компиляторов, которые анализируют исходный код и частично меняют порядок следования команд.

RISC-процессоры 3-го поколения

Самыми крупными разработчиками RISC-процессоров считаются Sun Microsystems (архитектура SPARC - Ultra SPARC), IBM (многокристальные процессоры Power, однокристальные PowerPC - PowerPC 620), Digital Equipment (Alpha - Alpha 21164), Mips Technologies (семейство Rxx00 -- R 10000), а также Hewlett-Packard (архитектура PA-RISC - PA-8000).

Все RISC-процессоры третьего поколения:

ü являются 64-х разрядными и суперскалярными (запускаются не менее 4-х команд за такт);

ü имеют встроенные конвейерные блоки арифметики с плавающей точкой;

ü имеют многоуровневую кэш-память. Большинство RISC-процессоров кэшируют предварительно дешифрованные команды;

ü изготавливаются по КМОП-технологии с 4 слоями металлизации.

Для обработки данных применяется алгоритм динамического прогнозирования ветвлений и метод переназначения регистров, что позволяет реализовать внеочередное выполнение команд.

Повышение производительности RISC-процессоров достигается за счет повышения тактовой частоты и усложнения схемы кристалла. Представителями первого направления являются процессоры Alpha фирмы DEC, наиболее сложными остаются процессоры компании Hewlett-Packard.

Уменьшение набора машинных команд в RISC-архитектуре позволило разместить на кристалле вычислительного ядра большое количество регистров общего назначения . Увеличение количества регистров общего назначения позволило минимизировать обращения к медленной оперативной памяти, оставив для работы с RAM только операции чтения данных из оперативной памяти в регистр и запись данных из регистра в оперативную память, все остальные машинные команды используют в качестве операндов регистры общего назначения.

Основными преимуществами RISC-архитектуры является наличие следующих свойств:

- Большое число регистров общего назначения.

- Универсальный формат всех микроопераций.

- Равное время выполнения всех машинных команд.

- Практически все операции пересылки данных осуществляются по маршруту регистр – регистр.

Равное время выполнения всех машинных команд позволяют обрабатывать поток командных инструкций по конвейерному принципу, т.е. выполняется синхронизация аппаратных частей с учетом последовательной передачи управления от одного аппаратного блока к другому.

Аппаратные блоки в RISC-архитектуре:

Блок загрузки инструкций включает в себя следующие составные части: блок выборки инструкций из памяти инструкций, регистр инструкций, куда помещается инструкция после ее выборки и блок декодирования инструкций. Эта ступень называется ступенью выборки инструкций.

Регистры общего назначения совместно с блоками управления регистрами образуют вторую ступень конвейера, отвечающую за чтение операндов инструкций. Операнды могут храниться в самой инструкции или в одном из регистров общего назначения. Эта ступень называется ступенью выборки операндов.

Арифметико-логическое устройство и, если в данной архитектуре реализован, аккумулятор, вместе с логикой управления, которая, исходя из содержимого регистра инструкций, определяет тип выполняемой микрооперации. Источником данных помимо регистра инструкций может быть счетчик команд, при выполнении микроопераций условного или безусловного перехода. Данная ступень называется исполнительной ступенью конвейера.

Набор состоящий из регистров общего назначения, логики записи и иногда из RAM образуют ступень сохранения данных. На этой ступени результат выполнения инструкций записываются в регистры общего назначения или в основную память.

Однако к моменту разработки RISC-архитектуры, промышленным стандартом микропроцессоров де-факто стала архитектура Intel x86, выполненная по принципу CISC-архитектуры. Наличие большого числа программ, написанных под архитектуру Intel x86, сделала невозможным массовый переход ЭВМ на RISC-архитектуру. По этой причине основной сферой использования RISC-архитектуры явились микроконтроллеры, благодаря тому, что они не были привязаны к существующему программному обеспечению. Кроме того некоторые производители ЭВМ во главе с IBM так же начали выпускать ЭВМ, построенные по RISC-архитектуре, однако несовместимость программного обеспечения между Intel x86 и RISC-архитектурой в значительной степени ограничивала распространение последних.

Однако, преимущества RISC-архитектуры были столь существенны, что инженеры нашли способ перейти на вычислители, выполненные по RISC-архитектуре, при этом не отказываясь от существующего программного обеспечения. Ядра большинство современных микропроцессоров, поддерживающих архитектуру Intel x86, выполнены по RISC-архитектуре с поддержкой мультискалярной конвейерной обработки. Микропроцессор получает на вход инструкцию в формате Intel x86, заменяем ее несколькими (до 4-х) RISC-инструкциями.

Таким образом, ядра большинства современных микропроцессоров, начиная с Intel 486DX, выполнены по RISC-архитектуре с поддержкой внешнего Intel x86 интерфейса. Кроме того, подавляющее большинство микроконтроллеров, а так же некоторые микропроцессоры выпускаются по RISC-архитектуре.

В современном RISC-процессоре используется не менее 32 регистров, часто более 100, в то время, как в классических ЦВМ обычно 8-16 регистров общего назначения. В результате процессор на 20%-30% реже обращается к оперативной памяти, что также повысило скорость обработки данных. Кроме того, наличие большого количества регистров упрощает работу компилятора по распределению регистров под переменные. Упростилась топология процессора, выполняемого в виде одной интегральной схемы, сократились сроки ее разработки, она стала дешевле.

После появления RISC-процессоров традиционные процессоры получили обозначение CISC – то есть с полным набором команд (Complete Instruction Set Computer).

В настоящее время RISC-процессоры получили широкое распространение. Современные RISC-процессоры характеризуются следующим:

- упрощенным набором команд;

- используются команды фиксированной длины и фиксированного формата,

простые способы адресации, что позволяет упростить логику декодирования команд;

- большинство команд выполняются за один цикл процессора;

- логика выполнения команд с целью повышения производительности ориентирована на аппаратную, а не на микропрограммную реализацию, отсутствуют макрокоманды, усложняющие структуру процессора и уменьшающие скорость его работы;

- взаимодействие с оперативной памятью ограничивается операциями

пересылки данных;

- для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки;

- создан конвейер команд, позволяющий обрабатывать несколько из них одновременно;

- наличие большого количества регистров;

- используется высокоскоростная память.

В RISC-процессорах обработка машинной команды разделена на несколько ступеней, каждую ступень обслуживают отдельные аппаратные средства и организована передача данных от одной ступени к следующей.

Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд.

Выполнение типичной команды можно разделить на следующие этапы:

ü выборка команды IF - по адресу, заданному счетчиком команд, из памяти извлекается команда;

ü 2) декодирование команды ID выяснение ее смысла, выборка операндов из регистров;

ü 3) выполнение операции EX, при необходимости обращения к памяти - вычисление физического адреса;

ü 4) обращение к памяти ME;

ü 5)запоминание результата WB

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК PIC16 и PIC17 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

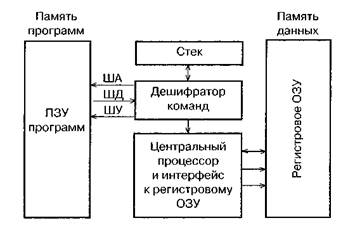

Рис.2 Структура МК с RISC архитектурой

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации оперрандов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению.

2.3 Микроконтроллер с RISC архитектурой

PIC16C71 относится к семейству КМОП микроконтроллеров. Отличается тем, что имеет внутреннее 1K x 14 бит EPROM для программ, 8-битовые данные и 64- байтовый встроенный аналого-цифровой преобразователь. Отличаются низкой стоимостью и высокой производительностью.

Пользователи, которые знакомы с семейством PIC16C5X могут посмотреть подробный список отличий нового от производимых ранее контроллеров.

Все команды состоят из одного слова (14 бит шириной) и исполняются за один цикл (200 нс при 20 МГц), кроме команд перехода, которые выполняются за два цикла (400 нс).

PIC16C71 имеет прерывание, срабатывающее от четырех источников, и восьмиуровневый аппаратный стек.

Периферия включает в себя 8-битный таймер/счетчик с 8-битным программируемым предварительным делителем (фактически 16 - битный таймер), 13 линий двунаправленного ввода/вывода и восьми битный АЦП. Высокая нагрузочная способность (25 мА макс. втекающий ток, 20 мА макс. Вытекающий ток) линий ввода/вывода упрощают внешние драйверы и, тем самым, уменьшается общая стоимость системы.

АЦП имеет четыре канала, схему выборки и хранения, разрешающую способность 8 бит с погрешностью не более одного младшего разряда. Среднее время преобразования 30 мкс, включая время выборки.

Серия PIC16C71 подходит для широкого спектра приложений от схем высокоскоростного управления автомобильными и электрическими двигателями до экономичных удаленных приемопередатчиков, показывающих приборов и связных процессоров. Наличие ПЗУ позволяет подстраивать параметры в прикладных программах (коды передатчика, скорости двигателя, частоты приемника и т.д.).

Малые размеры корпусов, как для обычного, так и для поверхностного монтажа, делает эту серию микроконтроллеров пригодной для портативных приложений.

Низкая цена, экономичность, быстродействие, простота использования гибкость ввода/вывода делает PIC16C71 привлекательным даже в тех областях, где ранее не применялись микроконтроллеры. Например, таймеры, замена жесткой логики в больших системах, сопроцессоры.

Микроконтроллер имеет:

- только 35 простых команд;

- все команды выполняются за один цикл(200ns), кроме команд перехода- 2 цикла;

- рабочая частота 0 Гц ... 20 МГц (min 200 нс цикл команды)

- 14- битовые команды;

- 8- битовые данные;

- 36 х 8 регистров общего использования;

- 15 специальных аппаратных регистров SFR;

- восьмиуровневый аппаратный стек;

- прямая, косвенная и относительная адресация данных и команд;

- четыре источника прерывания:

внешний вход INT

- переполнение таймера RTCC

- прерывание при завершении аналого-цифрового преобразования

- прерывание при изменении сигналов на линиях порта B.

Периферия, ввод и вывод микроконтроллера имеет:

- 13 линий ввода-вывода с индивидуальной настройкой;

- втекающий/вытекающий ток для управления светодиодами

- макс втекающий ток - 25 мА

- макс вытекающий ток - 20 мА

- 8 - битный таймер/счетчик RTCC с 8-битным программируемым предварительным делителем;

- модуль АЦП:

- 4 мультиплексируемых аналоговых входа, подсоединенных к одному аналога цифровому преобразователю

- схема выборки\хранения

- время преобразования - 20 мкс на канал

- преобразователь - 8 бит, с погрешностью +-1 LSB

- вход для внешнего опорного напряжения Vref (Vref <= Vdd)

- диапазон входных аналоговых сигналов от Vss до Vref

- автоматический сброс при включении;

- таймер включения при сбросе;

- таймер запуска генератора;

- Watchdog таймер WDT с собственным встроенным генератором, обеспечивающим повышенную надежность;

- EPROM бит секретности для защиты кода;

- экономичный режим SLEEP;

- выбираемые пользователем биты для установки режима возбуждения встроенного генератора:

- RC генератор RC

- обычный кварцевый резонатор XT

- высокочастотный кварцевый резонатор HS

- экономичный низкочастотный кристалл LP

- встроенное устройство самопрограммирования EPROM памяти программ,

используются только две ножки.

Обозначения ножек и их функциональное назначение:

RA4/RTCC -Вход через триггер Шмидта. Ножка порта ввода/вывода с открытым стоком или вход частоты для таймера/счетчика RTCC.

RA0/AIN0 - Двунаправленная линия ввода/вывода.

Аналоговый вход канала 0.

Как цифровой вход имеет уровни ТТЛ.

RA1/AIN1 -Двунаправленная линия ввода/вывода.

Аналоговый вход канала 1.

Как цифровой вход имеет уровни ТТЛ.

RA2/AIN2 -Двунаправленная линия ввода/вывода.

Аналоговый вход канала 2.

Как цифровой вход имеет уровни ТТЛ.

RA3/AIN3/Vref -Двунаправленная линия ввода/вывода.

RB0/INT -Двунаправленная линия порта вывода или внешний вход прерывания.

RB1 - RB5 -Двунаправленные линии ввода/вывода.

RB6 - Двунаправленные линии ввода/вывода.

RB7 -Двунаправленные линии ввода/вывода.

/MCLR/Vpp -Низкий уровень на этом входе генерирует сигнал сброса для контроллера. Активный низкий.

Вход через триггер Шмидта.

OSC1 -Для подключения кварца, RC или вход внешней тактовой частоты.

OSC2 -Генератор, выход тактовой

CLKOUT -частоты в режиме RC генератора, в остальных случаях - для подкл. кварца

Vdd –Напряжение питания.

Vss –Общий (земля).

Заключение

В данной курсовой работе рассмотрены микроконтроллеры с RISC и CISC архитектурой. RISC архитектура была рассмотрена более углубленно и точнее. Отмечена классификация, структура микроконтроллера, структура процессорного ядра микроконтроллера, основные особенности RISC архитектуры.

На сегодняшний день существует более 200 модификаций микроконтроллеров, совместимых с i8051, выпускаемых двумя десятками компаний, и большое количество микроконтроллеров других типов. Популярностью у разработчиков пользуются 8-битные микроконтроллеры PIC фирмы Microchip Technology и AVR фирмы Atmel, шестнадцатибитные MSP430 фирмы TI, а также ARM, архитектуру которых разрабатывает фирма ARM и продаёт лицензии другим фирмам для их производства, процессоров — микроконтроллеры.

При проектировании микроконтроллеров приходится соблюдать баланс между размерами и стоимостью с одной стороны и гибкостью и производительностью с другой. Для разных приложений оптимальное соотношение этих и других параметров может различаться очень сильно. Поэтому существует огромное количество типов микроконтроллеров, отличающихся архитектурой процессорного модуля, размером и типом встроенной памяти, набором периферийных устройств, типом корпуса и т. д.

Список использованной литературы:

1. «Основы микропроцессорной техники». Авторы Ю.В. Новиков и П.К Скоробогатов.

2. «Архитектура вычислительных систем» Москва «Радио и связь» 1990 г.

Автор А.Д. Смирнов.

3. «Электронно-вычислительные машины и системы» Москва «Радио и связь»1991г. авторы Б.М.Каган.

© 2010 Интернет База Рефератов