Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Реферат: Общие сведения о счетчиках

Реферат: Общие сведения о счетчиках

Общие сведения о счетчиках

Счётчики относятся к функциональным узлам последовательностного типа, логическое состояние которых определяется последовательностью поступления входных сигналов. Счётчики применяются в различных цифровых устройствах. Назначение счётчика очевидно: это подсчёт числа некоторых событий или временных интервалов, либо упорядочение событий в хронологической последовательности. Счётчики могут выполнять и другие функции, например, их можно использовать для адресации, в качестве делителей частоты и элементов памяти.

Счётчик характеризуются прежде всего модулем счёта (ёмкостью) М. Он переходит при поступлении входных сигналов из состояния в состояние, после каждых М сигналов возвращаясь к началу цикла. Счётчики классифицируют по значению модуля, направлению счёта, способу организации межразрядных связей, по способу подачи тактового импульса.

По значению модуля счёта различают двоичные (М=2n), двоично-кодированные (с произвольным модулем, но кодированием состояний двоичными кодами), счётчики с одинарным кодированием и др.

По направлению счёта счётчики делят на суммирующие (прямого счёта), вычитающие (обратного счёта) и реверсивные (с изменением направления счёта).

По способу организации межразрядных связей различают счётчики с последовательным, параллельным и комбинированными переносами. Параллельные счётчики называют синхронными, а последовательные - асинхронными.

Цифровую схему, выполняющую функцию счёта, можно собрать из триггеров. Рассмотрим некоторые схемы счётчиков.

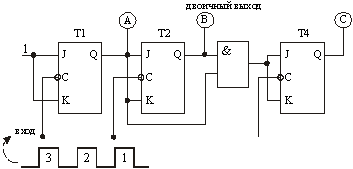

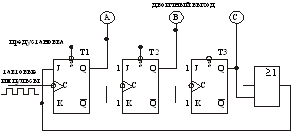

Счётчики со сквозным переносом

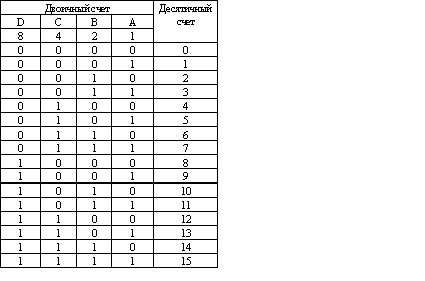

Процедура двоичного и десятичного счёта показана в табл. 13.1. Используя 4 двоичных разряда (D, C, B и A) можно считать от 0000 до 1111 (от 0 до 15 в десятичной системе). Столбец А соответствует самому младшему разряду, а столбец D самому старшему разряду. Если нужен счётчик, который считает от 0000 до 1111 (в двоичной системе), у него должно быть 16 различных выходных состояний, т.е. нужен счётчик с модулем 16. На рис.13.1 показана схема счётчика по модулю 16, составленная из 4 JK‑триггеров. Каждый JK‑триггер работает в режиме переключения (J=K=1). Пусть в начальный момент состояние выходов счётчика соответствует двоичному числу 0000 (счётчик очищен). При поступлении тактового импульса 1 на синхронизирующий вход (C) триггера T1 этот триггер переключается (при прохождении среза импульса) и на индикаторе появляется двоичное число 0001. Тактовый импульс 2 возвращает триггер T1 в исходное состояние 0 (Q=0), что в свою очередь приводит к переключению триггера T2 в состояние 1 (Q=1). На индикаторе появится число 0010. Счёт продолжается: срез сигнала на выходе каждого триггера запускает следующий триггер.

Таблица 13.1.

Таблица двоичного и десятичного счета

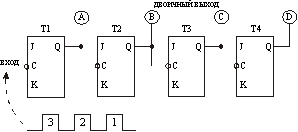

Рис.13.1. Схема счетчика по модулю 16

Из табл.13.1 видно, что цифры (1 или 0) в столбце А изменяется на каждом шаге счёта, т.е. триггер T1 переключается с приходом каждого нового тактового импульса. Из столбца В видно, что триггер T2 переключается в два раза реже триггера T1. Каждый более старший разряд «переключается» в 2 раза реже предыдущего.

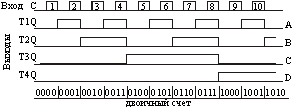

На рис.13.2 показаны временные диаграммы при работе счётчика в процессе счёта до 10 (двоичное число 1010).

Рис.13.2. Временные диаграммы работы счетчика по модулю 16

Синхронизирующему входу состветствует верхняя диаграмма. Диаграммы для выходов Q триггеров T1, T2, T3, T4 приведены ниже. Под диаграммами указаны двоичные числа, соответствующие различным состояниям счётчика. Из рис.13.2 видно, что тактовые импульсы запускают только триггер T1, триггер T1 запускает триггер T2, триггер T2 запускает триггер T3 и т.д. Каждый триггер воздействует только на один (следующий за ним триггер), поэтому для переключения всех триггеров необходимо некоторое время. Например, на импульсе 8 (рис.13.2) тактовый импульс запускает триггер T1, вызывая его переключение в состояние 0. Это в свою очередь приводит к переключению триггера T2 из состояния 1 в состояние 0. Затем точно также переключается T3. В момент установки на выходе Q триггера T3 уровня логического 0 запускается триггер T4, который переключается из состояния 0 в состояние 1. Таким образом, изменение состояний последовательно распространяется по цепочке триггеров. Рассматриваемый счётчик называют счётчиком со сквозным переносом. Кроме этого данный счётчик можно назвать асинхронным, поскольку предыдущий триггер вырабатывает для последующего тактовые импульсы. По направлению счёта счётчик, изображённый на рис.13.1 является суммирующим (прямого счёта).

Асинхронные счётчики по модулю 10

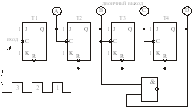

Счётчик по модулю 10 считает от 0000 до 1001 (от 0 до 9 в десятичной системе), т.е. до черты в табл.13.1. Для построения такого счётчика трёх триггеров недостаточно (10>23), поэтому он содержит 4 триггера, но имеет обратные связи, останавливающие счёт при коде 9=1001. На рис.13.3 показана схема счётчика по модулю 10, в которую кроме 4 триггеров включён логический элемент И‑НЕ, для установки всех триггеров в нулевое состояние (очистки счетчика) с приходом десятого импульса.

Рис.13.3. Схема асинхронного счетчика по модулю 10

Рассмотрим принцип работы данной схемы (рис.13.3). Из табл.13.1 видно, что за числом 1001 следует 1010 (10 в десятичной системе). При подаче логической 1, содержащейся в разрядах двоек и восьмерок двоичного числа 1010, на входы элемента И‑НЕ, этот элемент подаст логический 0 на входы R четырех триггеров. Таким образом, все триггеры установятся в состояние 0 и счетчик снова начинает считать от 0000 до 1010. Подобное использование логического элемента И‑НЕ позволяет создать счетчики с некоторыми другими значениями модуля. Счетчик, изображенный на рис.13.3 называют также декадным (десятичным) счетчиком.

Синхронные счетчики

В синхронных счетчиках все триггеры получают тактовый импульс одновременно, поскольку тактовые входы их соединяются параллельно. Такие триггеры переключаются практически одновременно. В асинхронных счетчиках каждый триггер вносит в процесс счета определенную задержку, поэтому младшие разряды результирующего кода появляются на выходах триггеров не одновременно, т.е. несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного асинхронного счетчика код 1111 появится на выходах триггеров уже после того, как поступит шестнадцатый тактовый импульс. Код 1111 сформируется не одновременно.

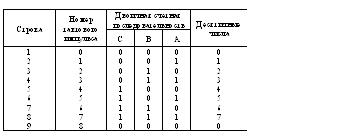

Рассмотрим схему 3‑разрядного счетчика по модулю 8 (рис.13.4). Все синхронизирующие входы триггеров (C) соединены параллельно, тактовые импульсы поступают непосредственно на синхронизирующий вход каждого триггера.

Рис.13.4. Схема синхронного счетчика по модулю 8

Последовательность двоичных чисел, проходимая счетчиком за один цикл счета (счетная последовательность) приведена в табл.13.2.

Таблица 13.2.

Счетная последовательность импульсов

Рассмотрим принцип работы данного счетчика в течение одного цикла счета. На каждом шаге цикла входной импульс поступает на синхронизирующий вход каждого триггера.

Импульс 1 строка 2 табл.13.2. Переключается только триггер T1, поскольку только у него на входах J и K действует уровень логической 1. T1 переходит из состояния 0 в состояние 1.

Результат: на выходе счетчика 001.

Импульс 2 строка 3. Переключаются два триггера T1 и T2, поскольку на входах J и K этих триггеров действует уровень логической 1. T1 переходит из состояния 1 в состояние 0, T2 — из состояния 0 в состояние 1.

Результат: на выходе 010.

Импульс 3 строка 4. Переключается только один триггер. T1 переходит из состояния 0 в состояние 1. T2 не переключается, поскольку на входах J и K действует уровень логического 0.

Результат: на выходе 011.

Импульс 4 строка 5. Все триггеры меняют свое состояние на противоположное. T1 и T2 переходят из 1 в 0. T3 переключается из 0 в 1.

Результат: на выходе 100.

Импульс 5 строка 6. Триггер T1 переходит из состояния 0 в состояние 1.

Результат: на выходе 101.

Импульс 6 строка 7. Переключаются два триггера. T1 переходит из 1 в 0, T2 - из 0 в 1.

Результат: на выходе 110.

Импульс 7 строка 8. Триггер T1 переходит из состояния 0 в состояние 1.

Результат: на выходе 111.

Импульс 8 строка 9. Все триггеры меняют свое состояние, переходя из 1 в 0.

Результат: на выходе 000.

Следует заметить, что в данном счетчике JK‑триггеры используются как в режиме переключения (J=K=1), так и в режиме блокировки (J=K=0).

Вычитающие счетчики

Помимо суммирующих счетчиков (прямого счета), рассмотренных выше, существуют счетчики которые считают в обратном направлении - вычитающие.

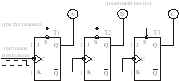

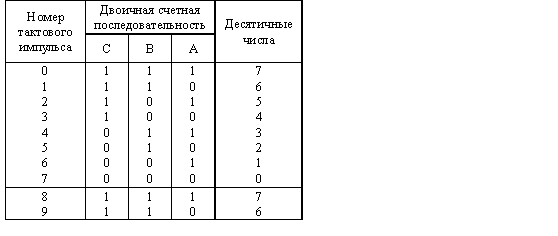

Рассмотрим схему асинхронного вычитающего счетчика по модулю 8 (рис.13.5).

Рис.13.5. Схема асинхронного вычитающего счетчика по модулю 1

Отличие данной схемы

от схемы суммирующего счетчика (рис.13.1) состоит в способе переноса сигнала от

триггера к триггеру. В суммирующем счетчике синхронизирующий вход каждого

триггера связан с прямым выходом Q предыдущего триггера. В вычитающем

счетчике синхронизирующий вход каждого триггера связан с инверсным выходом ![]() предыдущего

триггера. В счетчике изображенном на рис.13.5, перед началом счета в обратном

направлении предусмотрена предварительная его установка в состояние 111

(десятичное число 7) с помощью входа предустановки (S). Счетная

последовательность двоичных чисел приведена в табл.13.3.

предыдущего

триггера. В счетчике изображенном на рис.13.5, перед началом счета в обратном

направлении предусмотрена предварительная его установка в состояние 111

(десятичное число 7) с помощью входа предустановки (S). Счетная

последовательность двоичных чисел приведена в табл.13.3.

Таблица 13.3.

Счетная последовательность импульсов

Самоостанавливающиеся счетчики

Вычитающий счетчик, схема которого показана на рис.13.5 — счетчик циклического типа. Когда этот счетчик приходит в состояние 000, он снова начинает счет с двоичного числа 111. В некоторых случаях нужны счетчики, которые останавливаются, когда исчерпывается вся счетная последовательность. Рассмотрим, какие изменения нужно внести в схему вычитающего счетчика, чтобы счет прекращался при достижении состояния 000.

Рис.13.6. Схема самоостанавливающегося счетчика

Из рис.13.6 видно, что для этого нужно ввести в схему логический элемент ИЛИ, который будет устанавливать на входах J и K триггера T1 уровень логического 0, когда на выходах (C, B, A) счетчика появится сигнал 000. Если нужно начать новый цикл счета с двоичного числа 111, на вход предустановки S следует подать уровень логического 0.

Используя один логический элемент или их комбинацию, можно останавливать счет прямом и обратном направлении, на любом наперед заданном двоичном числе. Выход логического элемента нужно для этого присоединить к входам J и K первого триггера в асинхронном счетчике. При этом триггер T1 переводится в режим хранения.

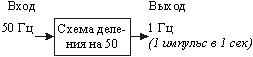

Счетчики — делители частоты

Одной из функций которую выполняют счетчики в цифровых системах, является деление частоты. Пример простой системы с делителем частоты показан на рис.13.7. Эта система составляет основу цифровых часов. Периодический сигнал электросети с частотой 50 Гц, сформированный в виде последовательности прямоугольных импульсов, подается на вход системы, которая делит частоту на 50.

Рис.13.7. Система с делителем частоты

На выходе схемы имеем последовательность прямоугольных импульсов с частотой 1 Гц (1 импульс в 1 сек). Это таймер секунд.

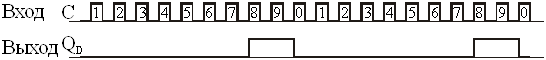

На рис.13.8 схематически изображен декадный счетчик, а на рис.13.9 приведены временные диаграммы для его синхронизирующего входа C и выхода QD, соответствующего двоичному разряду восьмерок.

Рис.13.8. Схема декадного счетчика

Рис.13.9. Временные диаграммы декадного счетчика

Из рис.13.9 видно, что 20 импульсов на входе счетчика преобразуются в 2 выходных импульса. Выполняется деление 20/2=10. Снимая сигнал с входа QD, декадного счетчика, получим счетчик‑делитель на 10. Т.е. частота выходного сигнала состовляет 1/10 частоты на входе счетчика.

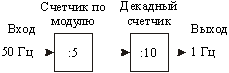

Последовательно соединяя рассмотренный декадный счетчик (счетчик‑делитель на 10) и по модулю 5 (счетчик‑делитель на 5) получим схему, осуществляющую деления частоты на 50. Структура такой схемы показана на рис.13.10. Последовательность прямоугольных импульсов с частотой 50 Гц поступает на вход счетчика - делителя на 5, а с его выхода с частотой 10 Гц подается на вход счетчика‑делителя на 10. На выходе схемы получим сигнал с частотой 1 Гц.

Рис.13.10. Структурная схема делителя частоты на 50

Функция деления частоты используется в таких цифровых устройствах, как частотомер, осциллограф и т.п.

Интегральные схемы счетчиков

На рис.13.11 представлена схема четырехразрядного двоичного счетчика‑делителя на 2, на 6 и на 12 (К155ИЕ4).

Рис.13.11. Схема четырехразрядного двоичного счетчика

Если подать тактовые импульсы с частотой f на вход С1, то на выходе А получим частоту f/2. Тактовые импульсы с частотой f на входе С2 запускают делитель на 6 и на выходе D имеем частоту f/6. При этом на выходах B и C имеем импульсы с частотой f/3. На выводы R1 и R2 подаются команды сброса. Для построения счетчика с модулем деления 12, требуется соединить делители на 1 и на 6, соединив выход А со входом С2. На вход С1 подается входная частота f, на выходе D получаем последовательность импульсов с частотой f/12.

Проектирование счетчиков

Рассмотрим пример структурного проектирования счетчиков. Выполним синтез структуры суммирующего синхронного (параллельного) счетчика по модулю 10 на JK‑триггерах. Следует отметить, что синхронные счетчики обычно строятся на базе RS, JK, D‑триггеров, синхронизируемых фронтом.

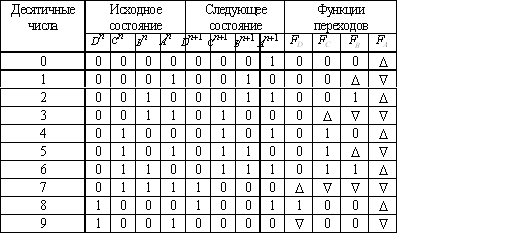

Для реализации счетчика требуется не менее 4 триггеров, поскольку трех триггеров недостаточно 23<10. Чтобы получить структуру с минимальным числом триггеров, примем m=4 (четырехразрядный счетчик). При этом 2m-M=24-10=6 состояний счетчика будут нештатаными. Рассмотрим таблицу состояний счетчика (табл. 13.4.), в которой в последних четырех столбцах показана функция переходов F для каждого разряда.

Таблица 13.4.

Таблица состояний счетчика

Функция переходов показывает изменения (или сохранения) состояния разряда в зависимости от значений управляющих сигналов. Эта функция принимает следующие значения

![]() переход из

состояния Qn=0 в Qn+1=1,

переход из

состояния Qn=0 в Qn+1=1,

![]() переход из

состояния Qn=1 в Qn+1=0,

переход из

состояния Qn=1 в Qn+1=0,

![]() сохранение

состояния Qn=Qn+1=0,

сохранение

состояния Qn=Qn+1=0,

![]() сохранение

состояния Qn=Qn+1=1.

сохранение

состояния Qn=Qn+1=1.

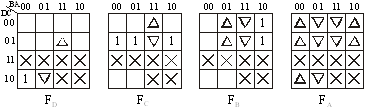

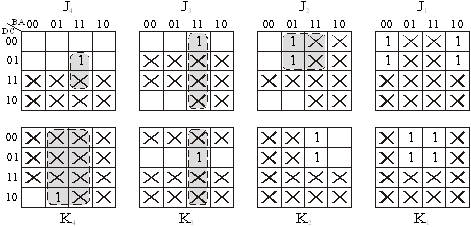

Используя таблицу состояний счетчика (табл. 13.4) для каждого разряда представляем функцию переходов в виде карты Карно (рис. 13.12).

Рис. 13.12. Карты Карно для функции переходов

В клетках карты указываются значения функции переходов. Знаком «X» обозначаются безразличные наборы, которые соответствуют нештатным состояниям счетчика.

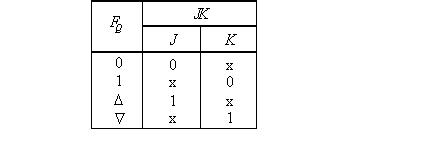

Определив для каждого из значений FQ соответствующие ему значения входных переменных J и K, получим словарь переходов JK‑триггера (табл. 13.5).

Таблица 13.5.

Словарь переходов JK-триггера

Используя словарь переходов JK‑триггера получаем карты Карно для функций входов J‑ и K‑триггеров в каждом разряде (рис. 13.13).

Рис. 13.13. Карты Карно для входов J и K триггеров

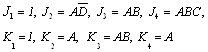

На основание карт Карно произведем минимизацию функции входов. В результате объединения клеток, показанных на рис. 13.13, получим простые выражения для функции входов

Рассмотрим более подробно минимизацию функции J4. Эта функция имеет восемь безразличных наборов, обозначенных «X» на рис. 13.13. Доопределим функцию таким образом, чтобы она имела значения J4=1 при ABCD=1111, выполним объединение клеток (рис. 13.13) и получим минимально дизъюктивную нормальную форму (МДНФ) в виде

J4=ABC.

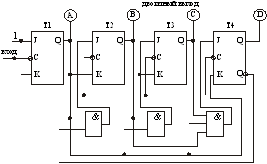

В соответствие с полученными выражениями для функции входов построим декадный счетчик (рис. 13.14).

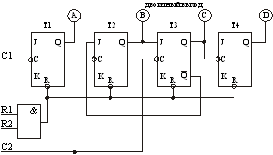

Рис. 13.14. Схема декадного счетчика

Из рис.13.14 видно, что схема декадного счетчика реализована на четырех триггерах и трех логических элементах И, два из которых имеют два входа и один имеет три входа. Счетчик, изображенный на рис. 13.14 является параллельным, т.к. все триггеры переключаются одновременно (синхронно).

© 2010 Интернет База Рефератов