Рефераты по сексологии

Рефераты по информатике программированию

Рефераты по биологии

Рефераты по экономике

Рефераты по москвоведению

Рефераты по экологии

Краткое содержание произведений

Рефераты по физкультуре и спорту

Топики по английскому языку

Рефераты по математике

Рефераты по музыке

Остальные рефераты

Рефераты по авиации и космонавтике

Рефераты по административному праву

Рефераты по безопасности жизнедеятельности

Рефераты по арбитражному процессу

Рефераты по архитектуре

Рефераты по астрономии

Рефераты по банковскому делу

Рефераты по биржевому делу

Рефераты по ботанике и сельскому хозяйству

Рефераты по бухгалтерскому учету и аудиту

Рефераты по валютным отношениям

Рефераты по ветеринарии

Рефераты для военной кафедры

Рефераты по географии

Рефераты по геодезии

Рефераты по геологии

Рефераты по геополитике

Рефераты по государству и праву

Рефераты по гражданскому праву и процессу

Рефераты по делопроизводству

Рефераты по кредитованию

Рефераты по естествознанию

Рефераты по истории техники

Рефераты по журналистике

Рефераты по зоологии

Рефераты по инвестициям

Рефераты по информатике

Исторические личности

Рефераты по кибернетике

Рефераты по коммуникации и связи

Учебное пособие: Синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Учебное пособие: Синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ

РОССИЙСКИЙ ХИМИКО-ТЕХНОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ

ИМ.Д.И. МЕНДЕЛЕЕВА

НОВОМОСКОВСКИЙ ИНСТИТУТ

Синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Методические указания

Под редакцией В.И. Воробьева

Новомосковск 2001

УДК 681.322

ББК 32.973

С 387

Рецензенты:

Кандитат технических наук, доцент кафедры "Автоматизация производственных процессов", НИ РХТУ им. Д.И. Менделеева, В.И. Иванков

Кандитат технических наук, доцент кафедры "Автоматизация производственных процессов", НИ РХТУ им. Д.И. Менделеева, В.З. Магергут

Составитель: Прохоров В.С.

С 387 Синтез схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором:

Методические указания / Под редакцией В.И. Воробьева.;

РХТУ им. Д.И. Менделеева, Новомосковский ин-т; Сост.:

В.С. Прохоров. - Новомосковск, 2001. - 28с.

В предлагаемом пособии даны описания и методические указания для выполнения индивидуального задания по курсу "Схематехника", которые помогут студентам ознакомиться с синтезом комбинационной схемы управления семисегментным индикатором.

Ил.7. Табл.7. Библиогр: 5 назв.

УДК 681.322

ББК 32.973

Содержание

Введение- 4

1. Порядок синтеза схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором- 5

2. Индивидуальное задание- 11

Приложение 1- 15

Приложение 2- 22

Библиографический список- 26

Введение

Логические элементы – основной “строительный материал цифровых систем обработки информации и управления.

Логические элементы выполняют простейшие логические операции (конъюнкцию, дизъюнкцию, инверсию) над входной информацией, представленной в двоичной форме. Однако реализация произвольного вычислительного процесса, содержащего арифметические операции (сложение, вычитание, умножение) или логические процедуры (поиск, сортировка, сравнение, сдвиг и др.), также осуществляются схемами, состоящими из логических элементов. Таким образом, логические элементы образуют универсальную среду, обеспечивающую арифметическую и логическую обработку входной двоичной информации.

Работа с логическими элементами требует не только знакомства с их принципиальными схемами и техническими характеристиками, но и знания основных положений алгебры логики, теории переключательных схем, а также умения по определенным правилам синтезировать логические схемы с заданными характеристиками. Выполнение предлагаемого задания позволит приобрести основные необходимые для инженера навыки.

1. Порядок синтеза схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Проиллюстрируем методику решения задачи на примере.

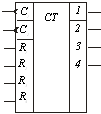

1. Входные данные вводятся в унитарном коде. Унитарный код двоичного n-разрядного числа представляется 2n разрядами, только один из которых равен 1. Для преобразования этого кода в двоичный код следует применить шифратор. Шифратор должен иметь десять входов, каждому из которых соответствует одно из чисел 0, 1, 2,...,9. Число 9 в двоичном коде представляется разрядами: 1001, т.е. шифратор должен иметь четыре выхода. В соответствии с этими требованиями составляют таблицу истинности (табл.1).

Таблица 1

Таблица истинности шифратора

| № |

Входные переменные |

Выходные переменные | ||||||||||||

| пп | x0 | x1 | x2 | x3 | x4 | x5 | x6 | x7 | x8 | x9 | y1 | y2 | y3 | y4 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 3 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 4 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 5 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 7 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 8 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 9 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

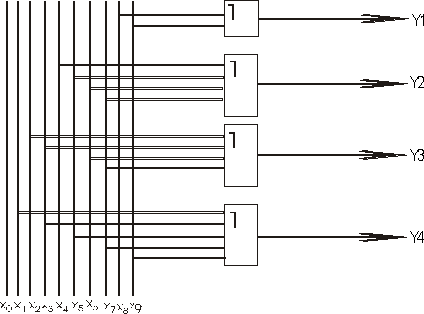

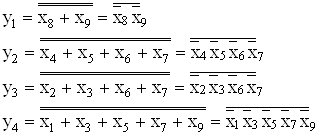

2. Получают логическую функцию шифратора в виде СДНФ путем записи “по единицам” (табл.1):

y1=x8+x9;

y2=x4+x5+x6+x7;

y3=x2+x3+x6+x7;

y4=x1+x3+x5+x7+x9

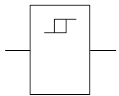

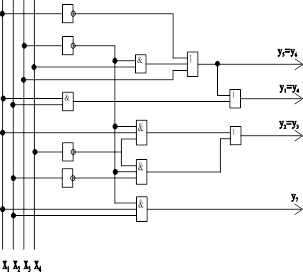

3. Используя полученные уравнения можно синтезировать функциональную схему шифратора в логическом базисе И, ИЛИ, НЕ (рис.1):

Рис.1. Функциональная схема шифратора на логических элементах или для синтеза шифратора в логических базисах И-НЕ или ИЛИ-НЕ следует применить закон двойной инверсии и закон инверсии (закон Де Моргана):

После выбора из табл.4 микросхем синтезируют принципиальную электрическую схему шифратора в заданном табл.5 базисе.

4. Допустим, что последние четыре цифры номера

зачетной книжки образуют число 3011, т.е. должны индицироваться только

стилизованные цифры 0, 1, 3, а при вводе остальных цифр - символ ![]()

5. При составлении таблицы истинности кодопреобразователя (табл.2) учитывают, что входные данные вводятся в двоичном коде, а наличие высокого потенциала на выходах кодопреобразователя y1, y2, y3,..., y7 вызывает свечение соответственно сегмента a, b, c, d, e, f, g 7-сегментного индикатора.

Таблица 2

Таблица истинности кодопреобразователя

| № | Входные | Выходные переменные | |||||||||

| пп | переменные | a | b | c | d | e | f | g | |||

| x4 | x3 | x2 | x1 | y1 | y2 | y3 | y4 | y5 | y6 | y7 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 3 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 5 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 7 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 8 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 9 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| 10. .15 | х | х | х | х | х | х | х | ||||

Символом “х” в табл. 2 обозначены безразличные состояния выходных переменных.

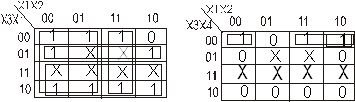

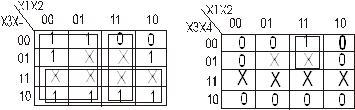

6. Для нахождения МДНФ применяют диаграммы Вейча-Карно (рис.2). Из табл.2 видно, что y1=y4; y2=y3; y5=y6.

![]()

![]()

![]()

![]()

Рис.2. Диаграммы Вейча-Карно для кодопреобразователя

На диаграммах Вейча-Карно безразличные состояния входных переменных, отмеченные символом “х” и включенные в контуры, считаются единичными, а вне контуров – нулевыми.

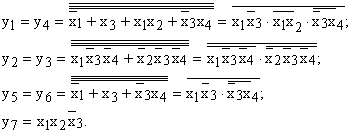

7. Для реализации функциональной схемы в базисе И-НЕ преобразуют полученные МДНФ, применяя законы двойной инверсии и инверсии (закон Де Моргана):

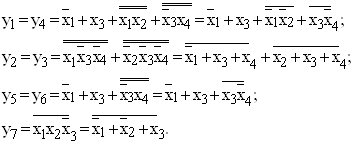

8. Для реализации функциональной схемы в базисе ИЛИ-НЕ преобразуют полученные МДНФ, применив указанные законы:

9. Схема кодопреобразователя в логическом базисе И, ИЛИ, НЕ (рис.3):

Рис.3. Функциональная схема кодопреобразователя в логическом базисе И, ИЛИ, НЕ

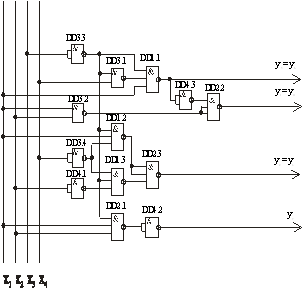

10. Схема кодопреобразователя в логическом базисе И-НЕ на логических элементах типа К176ЛА7 и К176ЛА9 (рис.4):

DD1, DD2: K176ЛА9 - 3х3 И-НЕ

DD3, DD4: K176ЛА7 - 4х2 И-НЕ

Рис.4. Принципиальная электрическая схема кодопреобразователя в логическом базисе И-НЕ

11. Так как между входом x3 и выходом y1 включено 5 логических элементов, то задержка кодопреобразователя равна

tз=5 tз. ср=5(200...300) =(1000...1500) нс.

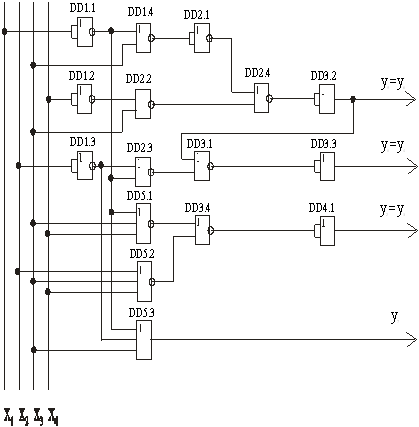

12. Схема кодопреобразователя в логическом базисе ИЛИ-НЕ на логических элементах типа К176ЛЕ5 и К176ЛЕ10 (рис.5):

DD1 – DD4: K176ЛЕ5 - 4х2 ИЛИ-НЕ

DD5: K176ЛЕ10 - 3х3 ИЛИ-НЕ

Рис.5. Принципиальная электрическая схема кодопреобразователя в логическом базисе ИЛИ-НЕ

13. Так как между входом x1 и выходом y1 включено 7 логических элементов, то задержка кодопреобразователя равна

tз=7(200...300) =(1400...2100) нс.

2. Индивидуальное задание

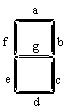

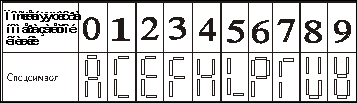

Синтезировать схему шифратора и кодопреобразователя, который управляет работой одноразрядного семисегментного индикатора. При этом должны индицироваться стилизованные цифры (Рис.6):

![]()

Рис.6. Стилизованные цифры 7-сегментного индикатора

Эти стилизованные цифры должны совпадать с четырьмя последними цифрами номера студенческого билета (зачетной книжки).

При поступлении на вход кодопреобразователя других цифровых данных должен высвечиваться спецсимвол, выбранный из табл.3.

Таблица 3

Спецсимвол

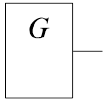

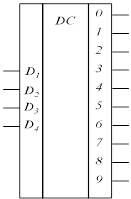

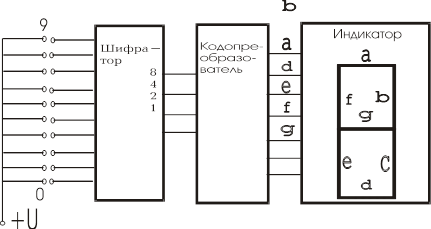

Входные данные в кодопреобразователь вводятся двоичным кодом, который получают из унитарного кода с помощью шифратора (рис.7).

Рис.7. Структурная схема шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором

Согласно варианту необходимо:

1. Составить таблицу истинности для шифратора.

2. Найти СДНФ шифратора.

3. Выбрать из табл.4 или табл. П2.2 подходящие ИМС и разработать на их основе принципиальную электрическую схему шифра в заданном базисе (табл.5).

Таблица 4

Рекомендуемый перечень микросхем

|

Условное обозначение ИМС | Состав и функциональное назначение ИМС | Тип логики | ||||

|

К155ЛА1 | 2х4 И-НЕ | ТТЛ | ||||

|

К155ЛА3 | 4х2 И-НЕ | ТТЛ | ||||

| К155ЛА4 | 3х3 И-НЕ | ТТЛ | |||||

| К155ЛЕ1 | 4х2 ИЛИ-НЕ | ТТЛ | |||||

| К176ЛЕ10 | 3х3 ИЛИ-НЕ | КМОП | |||||

| К176ЛЕ6 | 2х4 ИЛИ-НЕ | КМОП | |||||

| К176ЛЕ5 | 4х2 ИЛИ-НЕ | КМОП | |||||

| К176ЛА7 | 4х2 И-НЕ | КМОП | |||||

| К176ЛА8 | 2х4 И-НЕ | КМОП |

|

||||

| К176ЛА9 | 3х3 И-НЕ | КМОП |

|

||||

| К500ЛМ102 | 4х2 ИЛИ-НЕ | ЭСЛ |

|

||||

| К500ЛМ106 | 3х3 ИЛИ-НЕ | ЭСЛ |

|

||||

| К500ЛМ109 | 4 ИЛИ-НЕ, 5 ИЛИ-НЕ | ЭСЛ |

|

||||

| К561ЛЕ5 | 4х2 ИЛИ-НЕ | КМДП |

|

||||

| К561ЛЕ6 | 2х4 ИЛИ-НЕ | КМДП |

|

||||

| К561ЛА7 | 4х2 И-НЕ | КМДП |

|

||||

| К561ЛА8 | 2х4 И-НЕ | КМДП |

|

||||

| К561ЛА9 | 3х3 И-НЕ | КМДП |

|

||||

| К561ЛА10 | 3х3 ИЛИ-НЕ | КМДП |

|

||||

| К555ЛА3 | 4х2 И-НЕ | ТТЛШ |

|

||||

| К555ЛЕ1 | 4х2 ИЛИ-НЕ | ТТЛШ |

|

||||

| К555ЛН1 | 6 НЕ | ТТЛШ |

|

||||

| К555ЛИ1 | 4х2 И | ТТЛШ |

|

||||

| К555ЛИ3 | 3х3 И | ТТЛШ |

|

||||

| К555ЛА4 | 3х3 И-НЕ | ТТЛШ |

|

||||

| К555ЛА1 | 2х4 И-НЕ | ТТЛШ |

|

||||

| К555ЛЕ4 | 3х3 ИЛИ-НЕ | ТТЛШ |

|

||||

| К531ЛА3П | 4х2 И-НЕ | ТТЛШ |

|

||||

| К531ЛЕ1П | 4х2 ИЛИ-НЕ | ТТЛШ |

|

||||

| К531ЛН1П | 6 НЕ | ТТЛШ |

|

||||

| К531ЛИ3П | 3х3 И | ТТЛШ |

|

||||

|

К531ЛА1П | 2х4 И-НЕ | ТТЛШ |

|

|||

|

К531ЛА2П | 8 И-НЕ | ТТЛШ |

|

|||

Запись 2х4 И-НЕ означает, что в одном корпусе ИМС находятся два 4-входовых логических элемента И-НЕ. Более подробная информация о микросхемах ТЛЛ представлена в прил.2.

Таблица 5

Базис для синтеза шифратора

| Последняя цифра номера зачетной книжки | Четная | Нечетная |

| Базис | ИЛИ-НЕ | И-НЕ |

4. Определить время задержки для синтезированной схемы шифратора, используя данные табл.6 или табл. П2.1

Таблица 6

Время задержки

| Серия ИМС |

Время задержки, нс |

| К155 | 20 |

| К531 | 5 |

| К555 | 10 |

| К561 | 50 |

| К500 | 2 |

| К176 | 200 |

5. Составить таблицу истинности для кодопреобразователя.

6. С помощью диаграмм Вейча-Карно найти МДНФ для выходных переменных кодопреобразователя.

7. Выбрать из табл.4 или табл. П2.2 подходящие ИМС и разработать на их основе принципиальную электрическую схему кодопреобразователя в заданном в табл.7 базисе.

Таблица 7

Базис для синтеза кодопреобразователя

| Предпоследняя цифра номера зачетной книжки | Четная | Нечетная |

| Базис | ИЛИ-НЕ | И-НЕ |

8. Определить время задержки для синтезированной схемы кодопреобразователя.

9. Начертить полную принципиальную электрическую схему устройства. Принципиальную электрическую схему выполнить в соответствии ГОСТ 2.743-82 Обозначения условные графические в схемах. Элементы цифровой техники”. Можно использовать рекомендации Приложения 1.

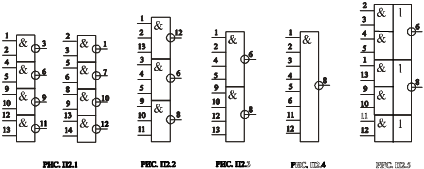

Приложение 1

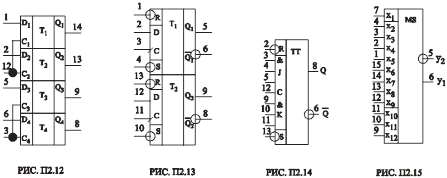

Двоичные логические элементы

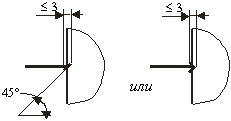

Общие принципы построения условных графических обозначений, а также условные графические обозначения двоичных логических элементов, выпускаемых промышленностью в виде цифровых микросхем, установлены ГОСТ 2.743-82.

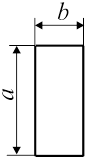

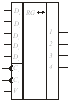

Условное графические обозначение двоичного логического элемента имеет форму прямоугольника, который может содержать три поля: основное и два дополнительных. В основном поле помещают информацию о функции, выполняемой логическим элементом - символ функции и при необходимости дополнительные данные по ГОСТ 2.304-68. В дополнительных полях помещают условные обозначения входов и выходов, называемые метками. Дополнительные поля и метки обычно имеют комбинационные и сложные логические элементы, у которых все входы (выходы) логически неравноценны. (См. табл. П.1.1, табл. П.1.2, табл. П.1.3, табл. П.1.4)

Все размеры условного графического обозначения по высоте должны быть кратны постоянной величине С. При этом расстояние между горизонтальной стороной прямоугольника и ближайшей входной (выходной) линией, а также между соседними входными (выходными) линиями должно быть не менее величины С. При ручном (неавтоматизированном) выполнении графического обозначения С³5 мм.

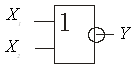

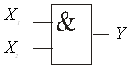

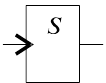

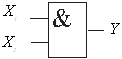

Таблица П.1.1

Символы логических операций

| Наименование | Обозна-чение | Наименование | Обозна-чение |

| ИЛИ | 1 | Регистр | RG |

| Монтажное ИЛИ |

1 |

Шифратор | CD |

| И | & | Дешифратор | DC |

| Монтажное И |

& |

Кодовый преобразователь | X/Y |

| Триггер | T | Сумматор | SM |

| Триггер двухступенчатый | TT | Пороговый элемент | |

| Продолжение табл. П.1.1 | |||

| Генератор | Г | Усилитель |

|

| Одновибратор | S | Формирователь сигнала | F |

|

Счетчик: а) двоичный |

СТ2 | Задержка временная | |

| б) десятичный | СТ10 | ||

Таблица П.1.2

Начертание условных обозначений цифровых микросхем

| Наименование | Обозначение |

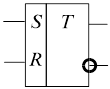

| Вход для раздельной установки триггера в состояние “1” (S-вход) | S |

| Вход для раздельной установки триггера в состояние “0” (R-вход) | R |

| Вход для установки состояния “1” в универсальном JK-триггере (J-вход) | J |

| Вход для установки состояния “0” в универсальном JK-триггере (К-вход) | K |

| Счетный вход (Т-вход) | T |

| Информационный вход для установки триггера в состояние “1” и “0” (D-вход) | D |

| Подготовительный управляющий вход для разрешения приема информации (V-вход) | V * |

| Исполнительный управляющий вход для осуществления приема информации. Вход синхронизации (С-вход) | C* |

1. Метки V и С применяют в комбинационных логических элементах для обозначения входов, подготавливающих и разрешающих выполнение логической операции.

2. При необходимости к буквам добавляют цифры, например

S1, S2, C1, C2 и т.д.3. Метки S, R, J, K, T, D, V и С -

начальные буквы английских слов.

Таблица П.1.3

Примеры условных обозначений логических элементов (*)

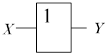

| Наименование | Обозначение |

|

Основное поле. Минимальные размеры, мм: a: 10 - 12 b: 8 - 12 При помещении дополнительных данных: a: 20 - 25 b: 12 - 17 |

|

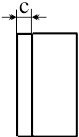

| Основное поле с левым дополнительным полем, c ³ 5 мм |

|

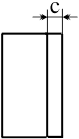

| Основное поле с правым дополнительным полем, c ³ 5 мм |

|

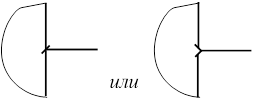

| Продолжение табл. П.1.3 | |

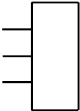

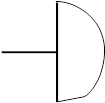

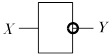

| Входы логического элемента |

|

| Выходы логического элемента |

|

| Прямой статический вход (фрагмент условного обозначения) |

|

| Прямой статический выход |

|

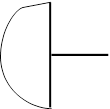

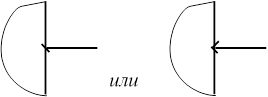

| Продолжение табл. П.1.3 | |

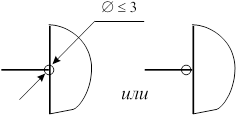

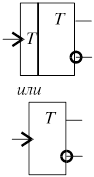

| Инверсный статический вход |

|

| Инверсный статический выход |

|

| Прямой динамический вход |

|

| Прямой динамический выход |

|

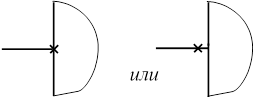

| Продолжение табл. П.1.3 | |

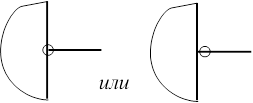

| Инверсный динамический вход |

|

| Инверсный динамический выход |

|

| Вывод, не несущий логической информации |

|

* Допускается ориентация условного графического обозначения, при котором входы располагаются сверху, а выходы - снизу.

Таблица П.1.4

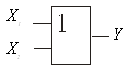

Примеры условных обозначений функциональных элементов

| Наименование | Обозначение | Наименование | Обозначение | |

|

Повтори- тель |

|

JK-триггер асинхронный |

|

|

| НЕ (инвертор) |

|

Т-триггер (триггер со счетным входом) |

|

|

|

ИЛИ (дизъюнк тор) |

|

D-триггер со статиче ским управле нием |

|

|

| ИЛИ-НЕ (элемент Приса) |

|

Цифровой элемент задержки |

|

|

|

И (конъюнк тор) |

|

Одновибратор с импульсным входом |

|

|

| Продолжение табл. П.1.4 | ||||

| И-НЕ (элемент Шеффера) |

|

Пороговый элемент (триггер Шмитта) |

|

|

|

RS-триггер асинхрон ный |

|

Регистр с реверсив ным сдвигом 4-разрядный |

|

|

| Генератор |

|

Счетчик двоично-десятич- ный 4-разряд- ный |

|

|

| Дешифратор на 4 разряда для газоразрядных индикаторов |

|

|||

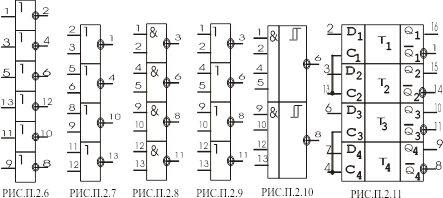

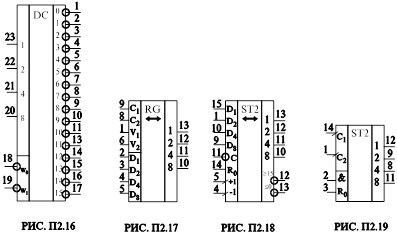

Приложение 2

Сведения о микросхемах ТТЛ серий 133, 134, 155 и 531

Таблица П.2.1

Электрические параметры базовых схем ТТЛ-типа

| Серия | |||

| Параметр | 133, 155 | 134 | 531 с диодами |

| Шотки | |||

|

Выходное напряжение “0”

Выходное напряжение “1”

Коэффициент разветвления по выходу Среднее время задержки Средняя статистическая мощность потребления, РПОТ, мВт, не более Частота переключений f, Мгц, не более |

0,4 2,4 10 20 (СН=15 пФ) 22 10 |

0,3 2,3 10 100 (СН=40 пФ) 2 3 |

0,5 2,7 10 5 (СН=15 пФ) 19 50 |

Таблица П.2.2

Функциональное назначение ИС ТТЛ

| Функциональное назначение | Обозначение |

Номер рисунка |

||

| Четыре логических элемента 2И-НЕ (133,155) | ЛА3 | П.1.1, а | ||

| Четыре логических элемента 2И-НЕ (134) | ЛБ1 | П.1., б | ||

| Три логических элемента 3И-НЕ (133, 155) | ЛА4 | П.1.2 | ||

| Два логических элемента 4И-НЕ (133, 155) | ЛА1 |

П.1.3 (для 155) |

||

| Продолжение табл. П.2.1 | ||||

| Два логических элемента 4И-НЕ (134) | ЛБ2 | - | ||

| Логический элемент 8И-НЕ (133, 134, 155) | ЛА2 | П.1.4 | ||

| Два логических элемента 2И-2ИЛИ-НЕ (133, 134, 155) | ЛР1 | П.1.5 | ||

| Триггер Шмитта с логическим элементом на шесть логических элементов НЕ (155) | ЛН1 | П.1.6 | ||

| Четыре логических элемента 2ИЛИ-НЕ (133, 155) | ЛЕ1 | П.1.7 | ||

| Четыре логических элемента 2И (133, 155) | ЛИ1 | П.1.8 | ||

| Два логических элемента 4И (155) | ЛИ6 | - | ||

| Четыре логических элемента 2ИЛИ (133, 155) | ЛЛ1 | П.1.9 | ||

| Два триггера Шмитта с логическим элементом на входе (133, 155) | ТЛ1 | П.1.10 | ||

| Четыре D-триггера с прямым и инверсным выходами (133, 155) | ТМ7 | П.1.11 | ||

| Четыре D-триггера (133, 155) | ТМ5 | П.1.12 | ||

| Два D-триггера (133, 134, 155) | ТМ2 | П.1.13 | ||

| JK-триггер с логикой на входе (133, 134, 155) | ТВ1 | П.1.14 (133,155) | ||

| Два JK-триггера (134) | ТВ14 | - | ||

| Четыре 2-входовых элемента “исключающее ИЛИ” (155) | ЛП5 | - | ||

| Селектор-мультиплексор на восемь каналов со стробированием (133, 155) | ЛП7 | П.1.15 | ||

| Дешифратор-демультиплексор четыре линии на 16 (133, 134, 155) | ИД3 | П.1.16 | ||

| Два 4-входовых расширителя по ИЛИ (133, 155) | ЛД1 | - | ||

| Одноразрядный полный сумматор (133, 155) | ИМ1 | - | ||

| Двухразрядный сумматор (133, 155) | ИМ2 | - | ||

| Четырехразрядный сумматор (133, 155) | ИМ3 | - | ||

| Одновибратор с логическим элементом на входе (133, 155) | АГ1 | - | ||

| Четырехразрядный универсальный сдвигающий регистр (133, 134, 155) | ИР1 | П.1.17 (133,155) | ||

| Реверсивный 8-разрядный регистр сдвига (133, 155) | ИР13 | - | ||

| Восьмиразрядная схема контроля четности и нечетности (134, 155) | ИП2 | - | ||

| Продолжение табл. П.2.1 | ||||

| Схема быстрого переноса для арифметическо-логического узла (134, 155) | ИП4 | - | ||

| Четырехразрядный двоичный реверсивный счетчик (133, 155) | ИЕ7 | П.1.18 | ||

| Двоичный счетчик (133, 134, 155) | ИЕП5 | П.1. 19 (133,155) | ||

| Двухразрядный сумматор (133, 155) | ИМ2 | - | ||

| Четырехразрядный сумматор (133, 155) | ИМ3 | - | ||

| Одновибратор с логическим элементом на входе (133, 155) | АГ1 | - | ||

Библиографический список

1. Калабеков Б.А., Мамзелев И.А. Цифровые устройства и микропроцессорные системы. – М.: Радио и связь, 1987. – 400 с.

2. Применение интегральных микросхем в ЭВТ / Данилов Р.В., Ельцова С.А., Иванов Ю.П. и др. – М.: Справочник. Радио и связь, 1987. – 384 с.

3. Проектирование импульсных и цифровых устройств радиотехнических систем: Учебное пособие / Под ред. Ю.М. Казаринова. – М.: Высшая школа, 1985. – 319 с.

4. Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. – Л.: Электроатомиздат, 1986. – 280 с.

5. Аналоговые и цифровые интегральные микросхемы: Справочное пособие / Под ред. С.В. Якубовского. – М.: Радио и связь, 1984. – 432 с.

© 2010 Интернет База Рефератов